# 6.S965 Digital Systems Laboratory II

Lecture 12

#### Administrative Stuff

- Last week of stuff (week 6) content was released Friday

- Try to do by the end of the week.

- Meant to have project survey out by last weekend but I fell behind. Plan:

- If you have a team of 2/3 you want to work with, email me the team.

- If you want to get partnered, email me with some ideas of what you want.

## Coverage

What is it? What does it mean?

## Coverage

tests=

Is concerned with how much have you tested a DUT

Some n-dimensional blob of possible module existence

#### The issue...

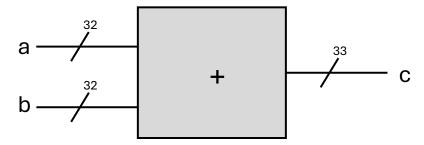

Consider a device that adds two 32 bit numbers.

- There are  $1.84 \times 10^{19}$  input possibilities, each with a correct output.

- If you verified 1 billion input/output combinations per second it would take ~600 years to fully verify the design

- And this is just a simple adder...

## And this gets astronomically worse as modules get more complicated

- ...especially as they get more stateful

- ...and with more inputs

- ...and with multiple sets of ports and things

## Can anything ever be fully covered?

- Some modules should be able to be almost fully covered

- Others maybe not, so you have to structure what you're looking for and zero in on important edge cases like:

- Max/min values, edge cases, overflow cases,

### What do you "cover"?

- If a module has clearly defined states, you should check to see those

- Maybe check to see how those states transition?

- Maybe check to see different sequences of input and/or output signals

- Check certain output signals against input signals

- Check sequences of inputs

- Check combinations of things listed above.

## Coverage is not necessarily about the verification of correct results

I mean it is an adjacent topic...

• But really the notion of coverage is meant to say how much was tested...with the assumption that it tested correctly.

It is also about exploring what/where your design can get to and can't get to.

### So let's look at an example...

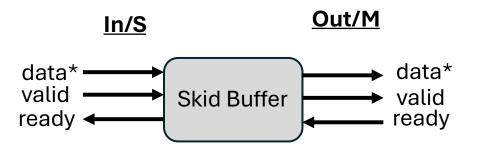

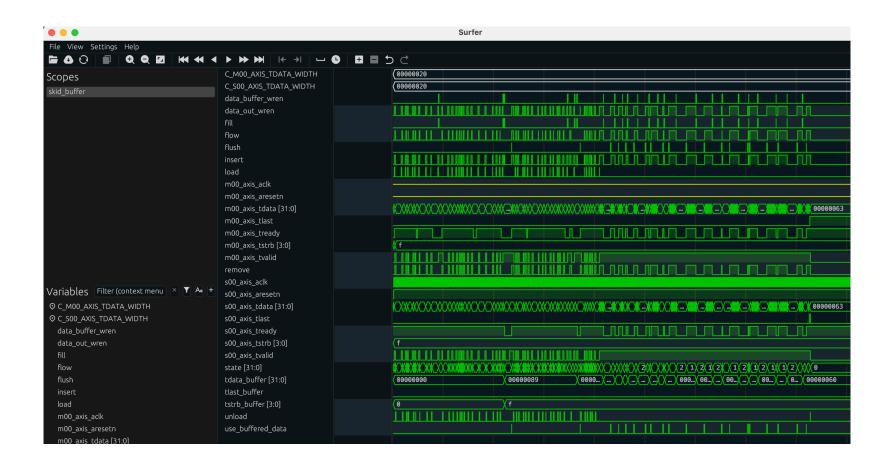

• We'll revisit the issue of TREADY propagation and build a module to handle that properly.

• The skid buffer fixes this...most of you are working on this right now.

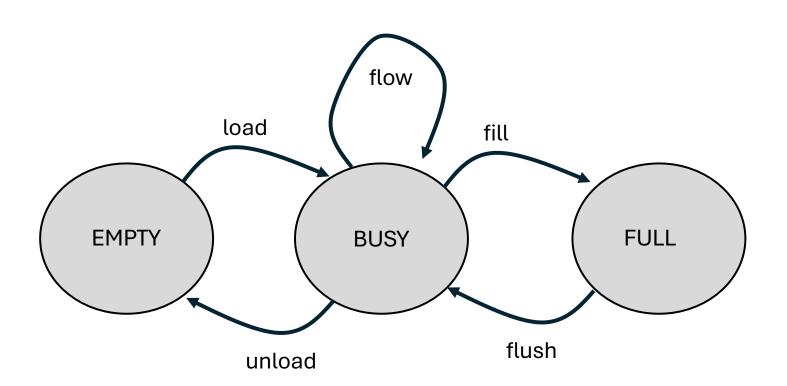

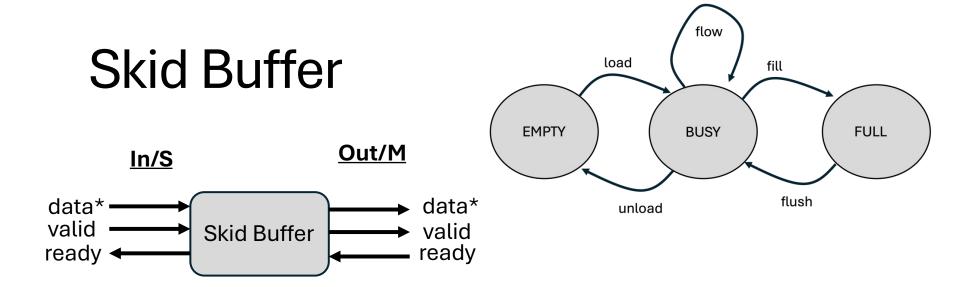

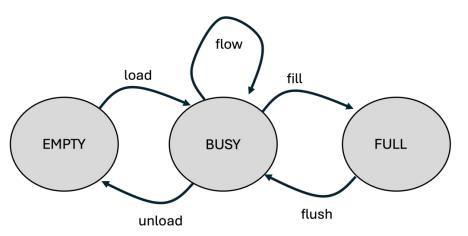

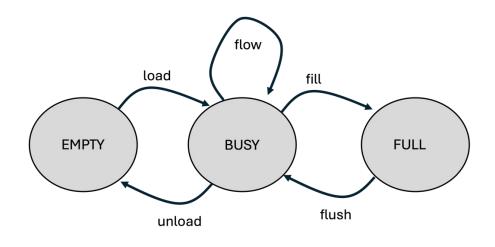

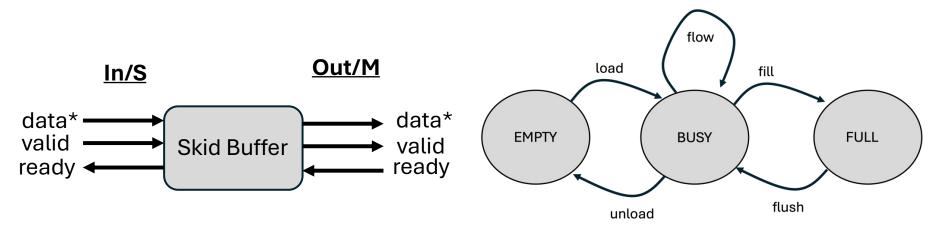

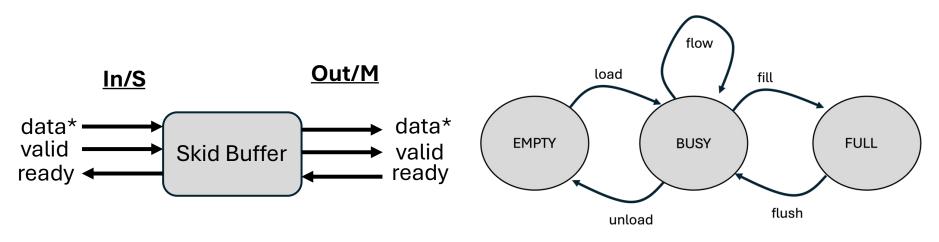

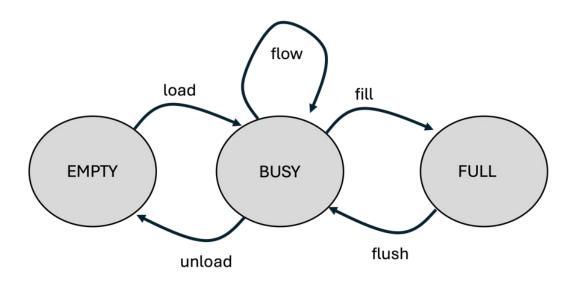

# Example: Skid Buffer

- BUSY is normal operation where data is coming in and out.

- If there's a hiccup on the output side, go to FULL and stall pipeline (s00\_tready > 0)

- If there's a hiccup on the input side, go to EMPTY and stall pipeline (m00\_tvalid → 0)

#### Skid Buffer

This simple FSM description...glossed over the potential complexity of the implementation: 3 states, each connected to 2 signals (valid/ready) per interface, for a total of 16 possible transitions out of each state, or 48 possible state transitions total.

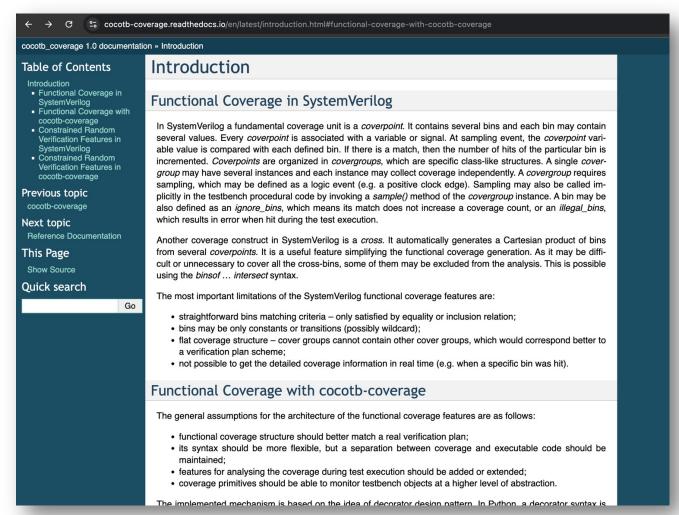

## Cocotb Coverage (version 1.2)

Install only

version 1.2

They updated to

support cocotb v

2.0

# Another library with ok docs and source code

## My Skid Buffer

• Most is hidden from you, but one thing to point out is there is an internal state variable.

```

enum { EMPTY, BUSY, FULL } state;

```

## Cocotb\_coverage

from cocotb\_coverage.coverage import CoverCross, CoverPoint, coverage\_db, coverage\_section import constraint

- Let's first focus on how we could measure the states that our system exists in?

- This thing has a very clearly defined state machine design and only certain states will connect to certain states

# First step is to define some coverage that we care about

Let's look at current state of our FSM and next/upcoming state of our FSM

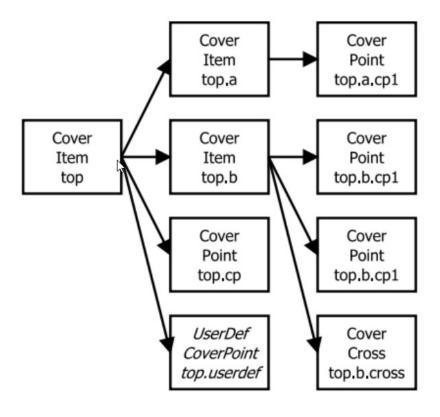

#### CoverPoint

- Object thar represents coverage. Concerned with a signal or combination of signals or state of being.

- Has a name (which you organize in a hierarchical fashion)

- Is used with a function you define

- Qualifies the inputs as one of the values specified in its bins argument

#### CoverCross

- CoverCross generates the Cartesian Product of multiple CoverPoints

- The CoverCross shown here will have how many possible bins?

### Coverage\_section

Is another object that represents a collection of coverpoints (and any related crosses)

The idea is to hierarchically organize the things you care about

## Must Sample/interface with the

actual DUT

Write a sampling function (just a passthrough here)

That is then called repeatedly in a monitor that is studying the state/next state on the rising clock edge Decorator links to coverage\_section by name...this is the function that is used by the cover points for analysis

```

ัดระ

def sampling function(s,ns):

pass

async def state monitor(dut):

states = {0: 'EMPT9', 1: 'BUS9', 2: 'FULL'}

read only = ReadOnly() #This is

falling edge = FallingEdge(dut.s00 axis aclk)

rising edge = RisingEdge(dut.s00 axis aclk)

await read only

old state = dut.state.value

while True:

await rising edge #when module would change

await read only

state = dut.state.value

sampling function(states[old state], states[state])

old state = state

```

#### Then run...

Launch state monitor here:

```

359 @cocotb.test()

360 async def test_a(dut):

361 """cocotb test for averager controller"""

362 inm = RXIS_Monitor(dut,'s00',dut.s00_axis_aclk,callback=j_math_model)

363 outm = RXIS_Monitor(dut,'m00',dut.s00_axis_aclk,callback=lambda x: sig_out_a

364 ind = M_RXIS_Driver(dut,'s00',dut.s00_axis_aclk) #M driver for 5 port

365 outd = S_RXIS_Driver(dut,'m00',dut.s00_axis_aclk) #5 driver for M port

366

367 # Create a scoreboard on the stream_out bus

368 scoreboard = Scoreboard(dut,fail_immediately=False)

369 scoreboard.add_interface(outm, sig_out_exp)

370 cocotb.start_soon(Clock(dut.s00_axis_aclk, 10, units="ns").start())

371

372 cocotb.start_soon(state_monitor(dut))

```

At end of test...report it out using coverage\_db.report\_coverage

```

coverage_db.report_coverage(cocotb.log.info, bins=True)

coverage_file = os.path.join(os.getenv('sim_result', "./"), 'coverage.xml')

coverage_db.export_to_xml(filename=coverage_file)

assert inm.transactions==outm.transactions, f"Transaction Count doesn't match! :/"

```

#### The result

```

top: <cocotb coverage.coverage.CoverItem object at 0x107301d10>, coverage=13, size=15

top.st : <cocotb coverage.coverage.CoverItem object at 0x10725e900>, coverage=13, size=15

top.st.next state : <cocobb coverage.coverage.CoverPoint object at 0x107301e50>, coverage=3, size=3

BIN EMPTY: 207

BIN BUSY : 162

BIN FULL: 131

top.st.state : <cocobb coverage.coverage.CoverPoint object at 0x10725e7b0>, coverage=12, size=12

BIN EMPTY: 207

BIN BUSY: 162

BIN FULL: 131

top.st.state.cross : <cocotb_coverage.coverage.CoverCross object at 0x10725ea50>, coverage=7, size=9

BIN ('EMPTY', 'EMPTY'): 158

BIN ('EMPTY', 'BUSY'): 49

BIN ('EMPTY', 'FULL') : 0

BIN ('BUSY', 'EMPTY'): 49

BIN ('BUSY', 'BUSY'): 90

BIN ('BUS9', 'FULL') : 23

BIN ('FULL', 'EMPTY'): 0

BIN ('FULL', 'BUS9') : 23

BIN ('FULL', 'FULL'): 108

test a passed

** TFST

STATUS SIM TIME (ns) REAL TIME (s) RATIO (ns/s) **

** test skid buffer.test a

PRSS.

5010.00

0.05

101040.37 **

** TESTS=1 PASS=1 FAIL=0 SKIP=0

5010.00

0.09

56264.42 **

```

### Or if you prefer to read xml

#### I guess

This XML file does not appear to have any style information associated with it. The document tree is shown below.

```

▼<top abs name="top" size="15" coverage="13" cover percentage="86.67">

▼<st size="15" coverage="13" cover percentage="86.67" abs name="top.st">

▼<state size="12" coverage="12" cover percentage="100.0" abs name="top.st.state" weight="1" at least="1">

<bin0 bin="EMPTY" hits="207" abs name="top.st.state.bin0"/>

<bin1 bin="BUSY" hits="162" abs_name="top.st.state.bin1"/>

<bin2 bin="FULL" hits="131" abs name="top.st.state.bin2"/>

▼<cross size="9" coverage="7" cover percentage="77.78" abs name="top.st.state.cross" weight="1" at least="1">

<bin0 bin="('EMPTY', 'EMPTY')" hits="158" abs name="top.st.state.cross.bin0"/>

<bin1 bin="('EMPTY', 'BUSY')" hits="49" abs name="top.st.state.cross.bin1"/>

<bin2 bin="('EMPTY', 'FULL')" hits="0" abs_name="top.st.state.cross.bin2"/>

<bin3 bin="('BUSY', 'EMPTY')" hits="49" abs name="top.st.state.cross.bin3"/>

<br/>

<bin4 bin="('BUSY', 'BUSY')" hits="90" abs name="top.st.state.cross.bin4"/>

<bin5 bin="('BUSY', 'FULL')" hits="23" abs name="top.st.state.cross.bin5"/>

<bin6 bin="('FULL', 'EMPTY')" hits="0" abs name="top.st.state.cross.bin6"/>

<bin7 bin="('FULL', 'BUSY')" hits="23" abs name="top.st.state.cross.bin7"/>

<bin8 bin="('FULL', 'FULL')" hits="108" abs name="top.st.state.cross.bin8"/>

</cross>

</state>

▼<next state size="3" coverage="3" cover percentage="100.0" abs name="top.st.next state" weight="1" at least="1">

<bin0 bin="EMPTY" hits="207" abs name="top.st.next state.bin0"/>

<bin1 bin="BUSY" hits="162" abs name="top.st.next state.bin1"/>

<bin2 bin="FULL" hits="131" abs name="top.st.next state.bin2"/>

</next state>

</st>

</top>

```

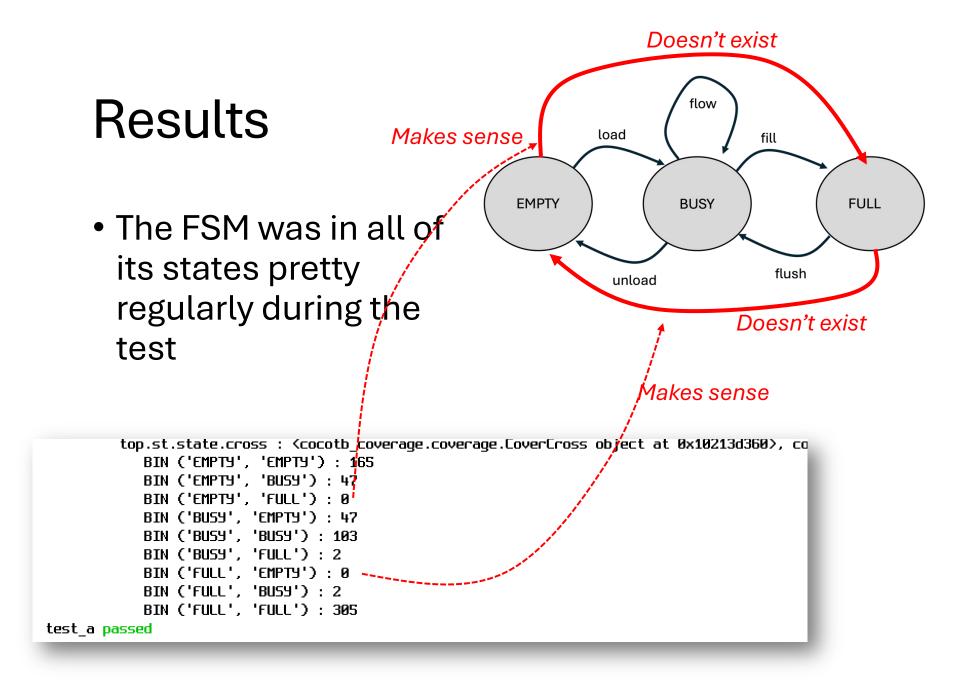

#### Results

The FSM was in all of its states pretty regularly during the test

```

top : <cocotb coverage.coverage.CoverItem object at 0x1029911e0>, coverage=13, size=15

top.st : <cocotb coverage.coverage.CoverItem object at 0x10213d3c0>, coverage=13, size=15

top.st.next state : <cocotb coverage.coverage.CoverPoint object at 0x102991390>, coverage=3, size=3

BIN EMPTY: 212

BIN BUSY: 152

BIN FULL: 307

top.st.state: <cocotb_coverage.coverage.CoverPoint object at 0x10213d390>, coverage=12, size=12

BIN EMPTY: 212

BIN BU59 : 152

BIN FULL: 307

top.st.state.cross : <cocotb coverage.coverage.CoverCross object at 0x10213d360>, coverage=7, size=9

BIN ('EMPTY', 'EMPTY'): 165

BIN ('EMPT9', 'BUS9'): 47

BIN ('EMPTY', 'FULL') : 0

BIN ('BUS9', 'EMPT9'): 47

BIN ('BUS9', 'BUS9'): 103

Potential issue?

BIN ('BUS9', 'FULL') : 2

BIN ('FULL', 'EMPTY'): 0

BIN ('FULL', 'BU59') : 2

BIN ('FULL', 'FULL') : 305

test a passed

```

### If you know things shouldn't happen

This does not mean you should ignore things that don't make sense...just things you've convinced yourself should not

## Can now target 100% coverage

• If you can prove through some mechanism or another which bins should be reachable and which are false or unachievable, then you can view your coverage more as a milestone

```

top : <cocotb coverage.coverage.CoverItem object at 0x104db5d10>, coverage=13, size=13

top.st : <cocotb coverage.coverage.CoverItem object at 0x104d16900>, coverage=13, size=13

top.st.next state : <cootb coverage.coverage.CoverPoint object at 0x104db5e50>, coverage=3, size=3

BIN EMPTY: 208

BIN BUSY: 163

BIN FULL: 129

top.st.state : <cocotb coverage.coverage.CoverPoint object at 0x104d167b0>, coverage=10, size=10

BIN EMPTY: 208

BIN BUSY : 163

BIN FULL: 129

top.st.state.cross : <cocotb coverage.coverage.CoverCross object at 0x104d16a50>, coverage=7, size=7

BIN ('EMPT9', 'EMPT9'): 163

BIN ('EMPT9', 'BUS9'): 45

BIN ('BUS9', 'EMPT9'): 45

BIN ('BUS9', 'BUS9'): 94

BIN ('BUS9', 'FULL'): 24

BIN ('FULL'. 'BUSY') : 24

BIN ('FULL', 'FULL'): 105

test a passed

```

Different tests but still you can see we got 100% coverage

### Further Pushing on this System

This simple FSM description...glossed over the potential complexity of the implementation: 3 states, each connected to 2 signals (valid/ready) per interface, for a total of 16 possible transitions out of each state, or 48 possible state transitions total.

### So let's do state and input

- Come up with STS covergroup (State and Signals)

- I want to look at the different states of my module as well as its exposure to different signal combinations on both S00 and M00 side

How many bins will this have?

```

STS = coverage section(

CoverPoint("top.st sig.state",

xf=lambda state,sig: state,

bins=['EMPT9', 'BUS9', 'FULL']

CoverPoint("top.st sig.s00 tvalid",

xf=lambda state,sig: sig.get('s00 tvalid'),

bins=[True, False]

CoverPoint("top.st sig.s00 tready",

xf=lambda state,sig: sig.get('s00 tready'),

bins=[True, False]

CoverPoint("top.st sig.m00 tvalid",

xf=lambda state,sig: sig.get('m00 tvalid'),

bins=[True, False]

CoverPoint("top.st sig.m00 tready",

xf=lambda state,sig: sig.get('m00 tready'),

bins=[True, False]

CoverCross("top.st sig.cross",

items=[ "top.st sig.state",

"top.st sig.s00 tvalid".

"top.st sig.s00 tready",

"top.st sig.m00 tvalid".

"top.st sig.m00 tready"]

```

## Write a quick monitor for it...

Instead of just feeding in state and old state now feed in state and all four valid/ready signals

Can run along side other coverage monitors

```

0STS

def sts sampling function(state,sig):

pass

async def state and input monitor(dut):

states = {0:'EMPT9', 1:'BUS9', 2:'FULL'}

read only = ReadOnly()

falling edge = FallingEdge(dut.s00 axis aclk)

rising edge = RisingEdge(dut.s00 axis aclk)

await read only

old state = dut.state.value

while Tone:

await falling_edge #when module would change

await read only

state = dut.state.value

sig = { 's00 tvalid':dut.s00 axis tvalid.value,

's00 tready':dut.s00 axis tready.value,

'm00 tvalid':dut.m00 axis tvalid.value,

'm00 tready':dut.m00 axis tready.value

sts sampling function(states[old state],sig)

old state = state

```

```

cocotb.start_soon(state_monitor(dut))

cocotb.start_soon(state_and_input_monitor(dut))

```

#### And Run It...

- Coverage is:

- 26/48 total

```

top.st sig.cross : <cocotb coverage.coverage.CoverCross object at 0x10700e350>, coverage=26, size=48

BIN ('EMPT9', True, True, True, True): 1

BIN ('EMPTY', True, True, True, False): 0

BIN ('EMPT9', True, True, False, True): 32

BIN ('EMPTY', True, True, False, False): 2

BIN ('EMPTY', True, False, True, True): 0

BIN ('EMPTY', True, False, True, False): 0

BIN ('EMPTY', True, False, False, True): 0

BIN ('EMPTY', True, False, False, False): 0

BIN ('EMPTY', False, True, True, True): 36

BIN ('EMPTY', False, True, True, False): 6

BIN ('EMPTY', False, True, False, True): 140

BIN ('EMPTY', False, True, False, False): 3

BIN ('EMPTY', False, False, True, True): 0

BIN ('EMPTY', False, False, True, False): 0

BIN ('EMPTY', False, False, False, True): 0

BIN ('EMPTY', False, False, False, False): 0

BIN ('BUS9', True, True, True, True): 63

BIN ('BUSY', True, True, True, False): 23

BIN ('BUSY', True, True, False, True): 4

BIN ('BUSY', True, True, False, False): 5

BIN ('BUS9', True, False, True, True): 1

BIN ('BUS9', True, False, True, False): 17

BIN ('BUSY', True, False, False, True): 0

BIN ('BUS9', True, False, False, False): 0

BIN ('BUSY', False, True, True, True): 3

BIN ('BUSY', False, True, True, False): 11

BIN ('BUSY', False, True, False, True): 29

BIN ('BUSY', False, True, False, False): 5

BIN ('BUS9', False, False, True, True): 1

BIN ('BUS9', False, False, True, False): 5

BIN ('BUSY', False, False, False, True): 0

BIN ('BUSY', False, False, False, False): 0

BIN ('FULL', True, True, True, True): 19

BIN ('FULL', True, True, True, False): 1

BIN ('FULL', True, True, False, True): 0

BIN ('FULL', True, True, False, False): 0

BIN ('FULL', True, False, True, True): 19

BIN ('FULL', True, False, True, False): 64

BIN ('FULL', True, False, False, True): 0

BIN ('FULL', True, False, False, False): 0

BIN ('FULL', False, True, True, True): 4

BIN ('FULL', False, True, True, False): 0

BIN ('FULL', False, True, False, True): 0

BIN ('FULL', False, True, False, False): 0

BIN ('FULL', False, False, True, True): 3

BIN ('FULL', False, False, True, False): 4

BIN ('FULL', False, False, False, True): 0

BIN ('FULL', False, False, False, False): 0

```

#### At the naïve level...

Yes there are 48 possible state transition and input combinations, but the state controls some of these signals, so that seems maybe a little excessive.

### Change the Crosses

There's likely no reason (at least at this point) to have the signals on both sides mixed together in one large coverage cross

```

STS = coverage section(

CoverPoint("top.st sig.state",

xf=lambda state,sig: state,

bins=['EMPT9', 'BUS9', 'FULL']

CoverPoint("top.st sig.s00 tvalid",

xf=lambda state,sig: sig.get('s00 tvalid'),

bins=[True, False]

),

CoverPoint("top.st sig.s00 tready",

xf=lambda state,sig: sig.get('s00 tready'),

bins=[True, False]

Э.

CoverPoint("top.st sig.m00 tvalid",

xf=lambda state,sig: sig.get('m00 tvalid'),

bins=[True, False]

CoverPoint("top.st_sig.m00_tready",

xf=lambda state,sig: sig.get('m00 tready'),

bins=[True, False]

CoverCross("top.st sig.scross",

items=[ "top.st sig.state",

"top.st sig.s00 tvalid",

"top.st sig.s00 tready"]

CoverCross("top.st sig.mcross",

items=[ "top.st siq.state",

"top.st sig.m00 tvalid",

"top.st sig.m00 tready"]

```

Only cross the state and values at each interface

#### Result

#### (STATE, VALID, READY)

#### Slave Cross:

```

top.st_sig.scross : <cocotb_coverage.coverage.CoverCross object at 0x10752e350>, coverage=10, size=12

BIN ('EMPTY', True, True) : 39

BIN ('EMPTY', True, False) : 0

BIN ('EMPTY', False, True) : 206

BIN ('BUSY', False, False) : 0

BIN ('BUSY', True, True) : 92

BIN ('BUSY', True, False) : 18

BIN ('BUSY', False, True) : 51

BIN ('BUSY', False, True) : 51

BIN ('BUSY', False, False) : 3

BIN ('FULL', True, True) : 19

BIN ('FULL', True, False) : 68

BIN ('FULL', False, False) : 2

BIN ('FULL', False, False) : 3

```

#### **Master Cross:**

(STATE, VALID, READY)

```

top.st_sig.mcross : (cocotb_coverage.coverage.CoverCross object at 0x10752e490), coverage=10, size=12

BIN ('EMPTY', True, True) : 41

BIN ('EMPTY', True, False) : 5

BIN ('EMPTY', False, True) : 182

BIN ('EMPTY', False, False) : 17

BIN ('BUSY', False, False) : 73

BIN ('BUSY', True, True) : 73

BIN ('BUSY', True, False) : 45

BIN ('BUSY', False, True) : 38

BIN ('BUSY', False, False) : 8

BIN ('BUSY', False, False) : 8

BIN ('FULL', True, True) : 36

BIN ('FULL', True, False) : 56

BIN ('FULL', False, True) : 0

BIN ('FULL', False, False) : 0

```

10/16/25 6.S965 Fall 2025 36

# Look at our design

- Some of these cross values should not be achieved :

- s00\_axis\_tready never be 0 in EMPTY

- m00\_axis\_tvalid never be 0 in FULL

#### Result

Legit/Might Occur:

✓

3

s00\_axis\_tready never 0 in EMPTY m00\_axis\_tvalid never 0 in FULL

Should Not Occur:

Slave Cross:

(STATE, VALID, READY)

```

top.st_sig.scross : <cocotb_coverage.coverage.CoverCross object at 0x10752e350>, coverage=10, size=12

▼ BIN ('EMPTY', True, True) : 39

N BIN ('EMPTY', True, False) : 0 ★

🔽 BIN ('EMPTY', False, True) : 206

🚫 BIN ('EMPTY', False, False) : 0 🔻

If I was previously EMPTY

V BIN ('BUS9', True, True) : 92

BIN ('BUSY', True, False): 18

there's no way READY would

🔽 BIN ('BUSY', False, True) : 51

🔽 BIN ('BUSY', False, False) : 3

be 0 now

BIN ('FULL', True, True): 19

BIN ('FULL', True, False): 68

BIN ('FULL', False, True): 2

BIN ('FULL', False, False): 3

```

#### **Master Cross:**

(STATE, VALID, READY)

```

top.st_sig.mcross : <cocotb_coverage.coverage.CoverCross object at 0x10752e490>, coverage=10, size=12

V BIN ('EMPTY', True, True) : 41

V BIN ('EMPTY', True, False) : 5

V BIN ('EMPTY', False, True) : 182

V BIN ('EMPTY', False, False) : 17

V BIN ('BUSY', True, True) : 73

V BIN ('BUSY', True, False) : 45

V BIN ('BUSY', False, True) : 38

V BIN ('BUSY', False, False) : 8

V BIN ('FULL', True, True) : 36

V BIN ('FULL', True, False) : 56

S BIN ('FULL', False, False) : 0

```

## Look at our design

- Some of these cross values should not be achieved :

- s00\_axis\_tready never 0 when was EMPTY

- m00\_axis\_tvalid never 0 when was FULL

# Point of Clarity...

Monitor uses previous state in combination with all four valid/ready signals

```

0STS

def sts sampling function(state,sig):

pass

async def state and input monitor(dut):

states = {0:'EMPT9', 1:'BUS9', 2:'FULL'}

read only = ReadOnly()

falling edge = FallingEdge(dut.s00 axis aclk)

rising_edge = RisingEdge(dut.s00_axis_aclk)

await read only

old_state = dut.state.value

while Tone:

await falling edge #when module would change

await read only

state = dut.state.value

sig = { 's00 tvalid':dut.s00 axis tvalid.value,

's00 tready':dut.s00 axis tready.value,

'm00 tvalid':dut.m00 axis tvalid.value,

'm00 tready':dut.m00 axis tready.value

sts sampling function(states[old state],sig)

old state = state

```

# Should these be achievable?

#### Slave Cross:

(OLD\_STATE, VALID, READY)

```

top.st_sig.scross : <cocotb_coverage.coverage.CoverCross object at 0x105555810>, coverage=10, size=12

▼ BIN ('EMPT9', True, True): 15

🚫 BIN ('EMPTY', True, False) : 0 🦶

☑ BIN ('EMPTY', False, True): 815

🔽 BIN ('BUSY', True, True) : 23

If I was previously EMPTY

🔽 BIN ('BUSY', True, False) : 29

there's no way READY would

🔽 BIN ('BUSY', False, True) : 18

🔽 BIN ('BUSY', False, False) : 4

be 0 now

🗸 BIN ('FULL', True, True) : 29

🗸 BIN ('FULL'. True. False) : 53

☑ BIN ('FULL', False, True) : 4

V BIN ('FULL'. False. False) : 11

```

#### **Master Cross:**

(OLD STATE, VALID, READY)

```

top.st_sig.mcross : <cocotb_coverage.coverage.CoverCross object at 0x105556350>, coverage=10, size=12

V BIN ('EMPTY', True, True) : ?

V BIN ('EMPTY', True, False) : 1

V BIN ('EMPTY', False, True) : 740

V BIN ('BUSY', False, False) : 82

V BIN ('BUSY', True, True) : 20

V BIN ('BUSY', True, False) : 46

V BIN ('BUSY', False, True) : 3

V BIN ('BUSY', False, False) : 5

V BIN ('FULL', True, True) : 40

V BIN ('FULL', True, False) : 57

S BIN ('FULL', False, True) : 0

S BIN ('FULL', False, False) : 0

```

# Ignore those...

#### Run again:

```

top.st sig.mcross : <cocotb coverage.coverage.CoverCross object at 0x106ffe490>, coverage=10, size=10

BIN ('EMPTY', True, True): 42

BIN ('EMPTY', True, False): 4

BIN ('EMPTY', False, True): 165

BIN ('EMPTY', False, False): 13

BIN ('BUS9', True, True): 72

Tests are doing

BIN ('BUSY', True, False): 40

BIN ('BUSY', False, True): 39

100% of coverage

BIN ('BUSY', False, False): 7

BIN ('FULL', True, True): 36

now

BIN ('FULL', True, False): 83

top.st sig.s00 tready : <cocotb coverage.coverage.CoverPoint object at 0x106bffe10>, coverage=2, size=2

BIN True : 382

BIN False: 119

top.st sig.s00 tvalid : <cocotb coverage.coverage.CoverPoint object at 0x106bfe3f0>, coverage=2, size=2

BIN True: 262

BIN False: 239

top.st sig.scross : <cocotb coverage.coverage.CoverCross object at 0x106ffe350>, coverage=10, size=10

BIN ('EMPTY', True, True): 38

BIN ('EMPTY', False, True): 186

BIN ('BUSY', True, True) : 93

BIN ('BUSY', True, False): 18

BIN ('BUSY', False, True): 45

BIN ('BUSY', False, False): 2

BIN ('FULL', True, True): 19

BIN ('FULL', True, False): 94

BIN ('FULL', False, True): 1

BIN ('FULL', False, False) : 5

42

```

## Another Big Issue

- AXI is about more than just the value at any point in time.

- As pointed out in class on Monday, AXI as a protocol has rules and those are rules are inherently stateful.

- Just throwing random values at the busses with no regard for history/meaning could be wrong:

- Giving it illegal values

- Wasting cycles testing stuff that shouldn't be tested

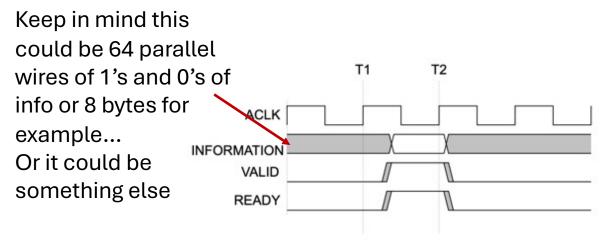

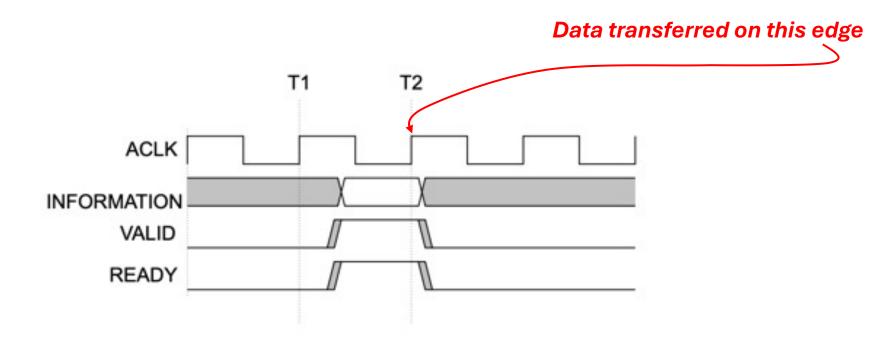

#### **Generalized Transaction**

- All Channel Interactions follow same high-level structure

- Data is handed off IF AND ONLY IF VALID and READY are high on the rising edge of the clock

- If that happens, both parties must realize that data transfer has happened

Figure A3-4 VALID with READY handshake

### **VALID** then READY

- Valid can be high first

- Then ready can show up later

- Only when both are high is data exchanged

Figure A3-2 VALID before READY handshake

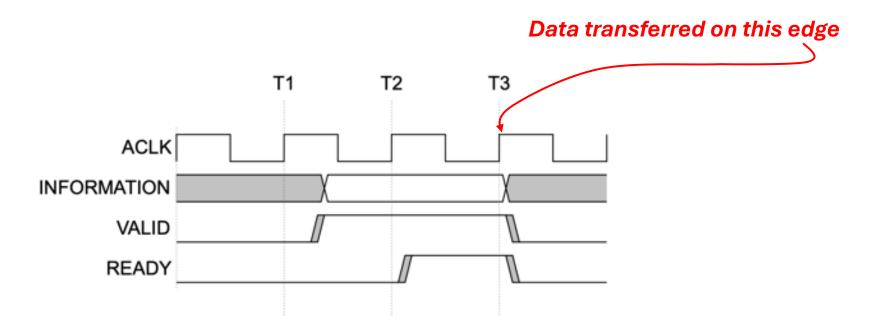

### **READY then VALID**

- Ready can be high first

- Then Valid can show up later

- Only when both are high is data exchanged

Figure A3-3 READY before VALID handshake

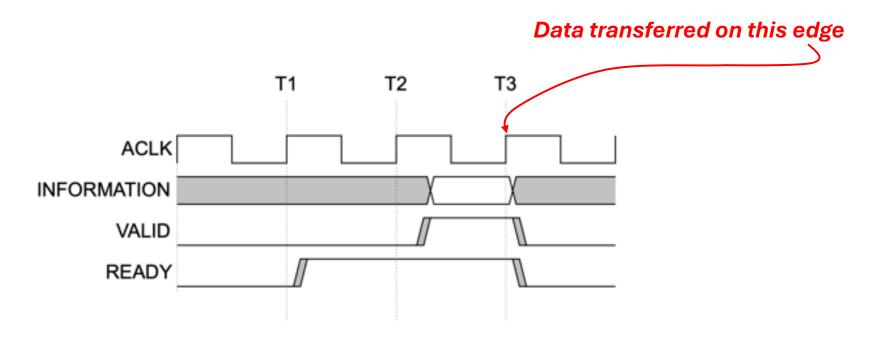

#### READY WITH VALID

- Ready and Valid come high at the same time

- Totally allowed

- Data is exchanged on that clock edge

Figure A3-4 VALID with READY handshake

#### **IMPORTANT**

- the VALID signal of the AXI interface sending information must not be dependent on the READY signal of the AXI interface receiving that information

- an AXI interface that is receiving information may wait until it detects a VALID signal before it asserts its corresponding READY signal.

- In other words **READY** can depend on **VALID**, but not the other way around.

- Once VALID is asserted, it cannot be deasserted until READY has also been asserted for at least one cycle

# Make a New "higher level" Cover

section

This one will track cycle-to-cycle transitions of the valid and ready signals on both ports

No reason to combine the two ports really...there's nothing about the spec anyways

```

OS = coverage section(

CoverPoint("top.os.s00 tvalid",

xf=lambda sig: sig.get('s00 tvalid'),

bins=['V:0->0', 'V:0->1', 'V:1->0', 'V:1->1']

CoverPoint("top.os.s00 tready",

xf=lambda siq: siq.qet('s00 tready'),

bins=['R:0->0', 'R:0->1', 'R:1->0', 'R:1->1']

CoverPoint("top.os.m00 tvalid",

xf=lambda sig: sig.get('m00 tvalid'),

bins=['V:0->0','V:0->1','V:1->0','V:1->1']

CoverPoint("top.os.m00 tready",

xf=lambda sig: sig.get('m00 tready'),

bins=['R:0->0', 'R:0->1', 'R:1->0', 'R:1->1']

CoverCross("top.os.s cross",

items=[ "top.os.s00 tvalid",

"top.os.s00 tready"]

CoverCross("top.os.m cross",

items=[ "top.os.m00 tvalid",

"top.os.m00 tready"]

```

# Make support functions

Track and Label transitions of all four signals over time.

```

async def os monitor(dut):

read only = ReadOnly()

falling edge = FallingEdge(dut.s00 axis aclk)

rising edge = RisingEdge(dut.s00 axis aclk)

await read only

olds = get rv(dut)

while True:

await falling edge #when module would change

await read only

news = get rv(dut)

sig = {}

for i in ['s00 tvalid','s00 tready','m00 tvalid','m00 tready']:

if 'v' in i:

sig[i] = 'V:'+match(olds[i],news[i])

sig[i] = 'R:'+match(olds[i],news[i])

os sampling function(sig)

olds = news # remember for future compare

```

```

def match(old,new):

outstr = ''

if old:

outstr+='1'

else:

outstr+='0'

outstr += '->'

if new:

outstr+='1'

else:

outstr+='0'

return outstr

```

#### **RUN**

## Run it and you get...

```

top.os.s cross: <cocotb coverage.coverage.CoverCross object at 0x10306c2b0>, coverage=10, size=16

BIN ('V:0->0', 'R:0->0') : 0

BIN ('V:0->0', 'R:0->1') : 1

BIN ('V:0->0', 'R:1->0'): 0

BIN ('V:0->0', 'R:1->1'): 198

BIN ('V:0->1', 'R:0->0') : 2

BIN ('V:0->1', 'R:0->1') : 0

BIN ('V:0->1', 'R:1->0'): 0

BIN ('V:0->1', 'R:1->1') : 49

BIN ('V:1->0', 'R:0->0') : 0

BIN ('V:1->0', 'R:0->1') : 0

BIN ('V:1->0', 'R:1->0') : 3

BIN ('V:1->0', 'R:1->1') : 48

BIN ('V:1->1', 'R:0->0'): 83

BIN ('V:1->1', 'R:0->1') : 18

BIN ('V:1->1', 'R:1->0') : 16

BIN ('V:1->1', 'R:1->1') : 83

top.os.m cross: <cocotb coverage.coverage.CoverCross object at 0x10306c3e0>, coverage=12, size=16

BIN ('V:0->0', 'R:0->0') : 22

BIN ('V:0->0', 'R:0->1'): 4

BIN ('V:0->0', 'R:1->0') : 0

BIN ('V:0->0', 'R:1->1') : 161

BIN ('V:0->1', 'R:0->0') : 4

BIN ('V:0->1', 'R:0->1') : 2

BIN ('V:0->1', 'R:1->0') : 0

BIN ('V:0->1', 'R:1->1') : 39

BIN ('V:1->0', 'R:0->0') : 0

BIN ('V:1->0', 'R:0->1') : 0

BIN ('V:1->0', 'R:1->0') : 9

BIN ('V:1->0', 'R:1->1') : 36

BIN ('V:1->1', 'R:0->0') : 99

BIN ('V:1->1', 'R:0->1') : 20

BIN ('V:1->1', 'R:1->0') : 16

BIN ('V:1->1', 'R:1->1') : 89

```

### Let's Consider Slave Side

Legit/Might Occur:

✓

Should Not Occur:

Both these are situations where the Valid is deasserting before a handshake occurred

```

top.os.s_cross : <cocotb_coverage.c

▼ BIN ('V:0->0', 'R:0->0') : 0

▼ BIN ('V:0->0', 'R:0->1') : 1

▼ BIN ('V:0->0', 'R:1->0') : 0

BIN ('V:0->0', 'R:1->1') : 198

▼ BIN ('V:0->1', 'R:0->0') : 2

▼ BIN ('V:0->1', 'R:0->1') : 0

BIN ('V:0->1', 'R:1->0') : 0

BIN ('V:0->1', 'R:1->1'): 49

BIN ('V:1->0', 'R:0->0') : 0

BIN ('V:1->0', 'R:0->1') : 0

▼ BIN ('U:1->0'. 'R:1->0') : 3

✓ BIN ('V:1->0', 'R:1->1'): 48

▼ BIN ('V:1->1', 'R:0->0') : 83

✓ BIN ('V:1->1', 'R:0->1') : 18

▼ BIN ('V:1->1', 'R:1->0') : 16

▼ BIN ('V:1->1', 'R:1->1') : 83

```

# So what should we be concerned about?

Legit/Might Occur:

Should Not Occur:

```

top.os.s cross : <cocotb coverage.c

▼ BIN ('V:0->0', 'R:0->0') : 0

▼ BIN ('U:0->0'. 'R:0->1') : 1

☑ BIN ('V:0->0', 'R:1->0') : 0 !!

☑ BIN ('V:0->0', 'R:1->1') : 198

☑ BIN ('V:0->1', 'R:0->0') : 2

☑ BIN ('V:0->1', 'R:0->1') : 0 !!

☑ BIN ('V:0->1', 'R:1->0') : 0 👭

▼ BIN ('U:0->1'. 'R:1->1'): 49

○ BIN ('V:1->0'. 'R:0->0') : 0

○ BIN ('V:1->0'. 'R:0->1') : 0

☑ BIN ('V:1->0', 'R:1->0') : 3

☑ BIN ('V:1->0', 'R:1->1') : 48

▼ BIN ('V:1->1', 'R:0->0') : 83

☑ BIN ('V:1->1', 'R:0->1') : 18

☑ BIN ('V:1->1', 'R:1->0') : 16

☑ BIN ('V:1->1'. 'R:1->1') : 83

```

# Similarly on Master Side:

Legit/Might Occur:

Should Not Occur:

This is actually pretty reassuring since our DUT would be the device that would actually be causing these violations

```

top.os.m cross : <cocotb coverage.

▼ BIN ('V:0->0', 'R:0->0') : 22

✓ BIN ('V:0->0',

'R:0->1') : 4

☑ BIN ('V:0->0', 'R:1->0') :

☑ BIN ('V:0->0', 'R:1->1') : 161

▼ BIN ('V:0->1', 'R:0->0')

☑ BIN ('V:0->1', 'R:0->1') : 2

☑ BIN ('V:0->1', 'R:1->0') : 0

☑ BIN ('V:0->1', 'R:1->1') : 39

BIN ('V:1->0', 'R:0->0')

BIN ('V:1->0', 'R:0->1') : 0

BIN ('V:1->0',

'R:1->0')

BIN ('V:1->0', 'R:1->1')

BIN ('V:1->1', 'R:0->0') : 99

BIN ('V:1->1', 'R:0->1') : 20

BIN ('V:1->1', 'R:1->0') : 16

BIN ('V:1->1', 'R:1->1'): 89

```

#### Conclusions?

So probably more read toggling in our testbench would be good to be honest.

```

top.os.s cross : <cocotb coverage.c

▼BIN ('V:0->0', 'R:0->0') : 0

☑BIN ('V:0->0', 'R:0->1'): 1

'R:1->0') :

☑ BIN ('V:0->0'.

▼BIN ('V:0->0',

'R:1->1'

▼ BIN ('V:0->1'.

'R:0->0')

☑ BIN ('V:0->1'.

'R:0->1')

☑ BIN ('U:0->1', 'R:1->0

☑ BIN ('U:0->1'. 'R:1->1

○ BIN ('V:1->0'.

'R:0->0')

○ BIN ('V:1->0'.

'R:0->1')

☑ BIN ('V:1->0',

'R:1->0')

Ⅵ RTN ('U:1->A'.

'R:1->1')

☑BIN ('V:1->1', 'R:0->0') : 83

Ⅵ RTN ('V:1->1'.

'R:0->1')

☑ BIN ('V:1->1',

'R:1->0')

☑BIN ('V:1->1', 'R:1->1') : 83

```

```

top.os.m_cross : <cocotb_coverage.</pre>

☑ BIN ('V:0->0', 'R:0->0') : 22

✓ BIN ('V:0->0', 'R:0->1'): 4

✓ BIN ('V:0->0', 'R:1->0') : 0

✓

▼ RIN ('U:0->0'. 'R:1->1')

☑ BIN ('V:0->1'.

■ BIN ('V:0->1',

'R:0->1')

BIN ('V:0->1', 'R:1->0')

BIN ('V:0->1', 'R:1->1') :

BIN ('V:1->0'.

'R:0->0')

BIN ('V:1->0'.

'R:0->1') :

BIN ('V:1->0', 'R:1->0') :

BIN ('V:1->0'. 'R:1->1')

BIN ('V:1->1'.

'R:0->0') :

'R:0->1')

BIN ('V:1->1', 'R:1->0') : 16

BIN ('V:1->1', 'R:1->1'): 89

```

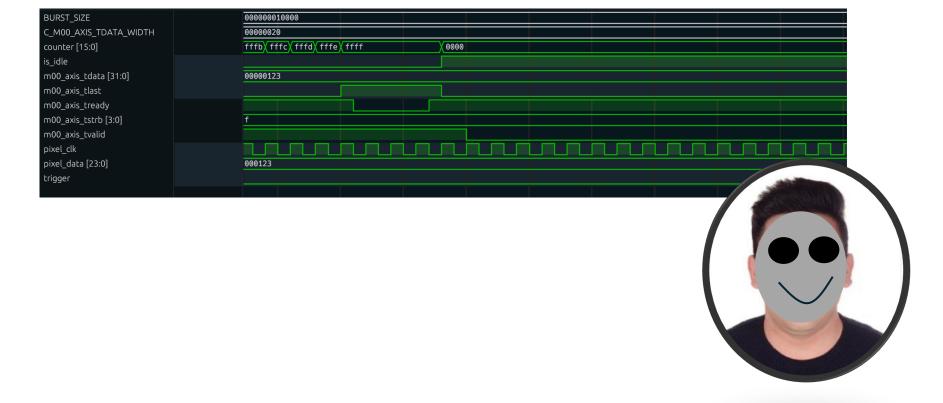

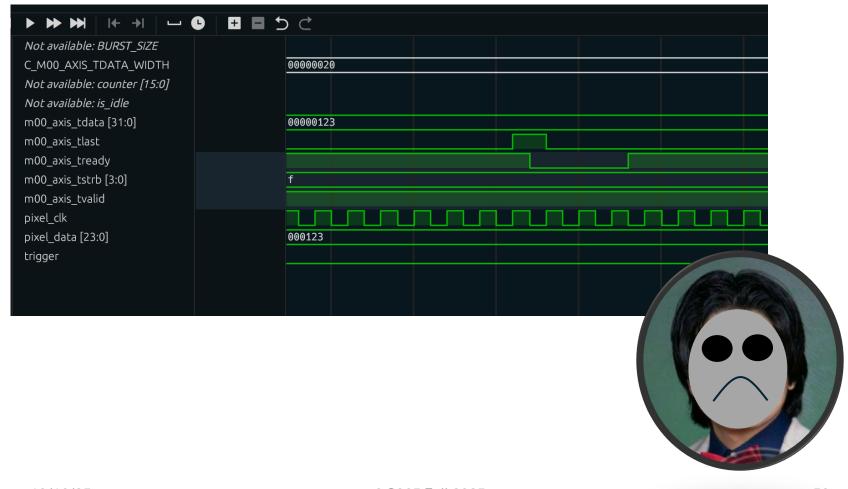

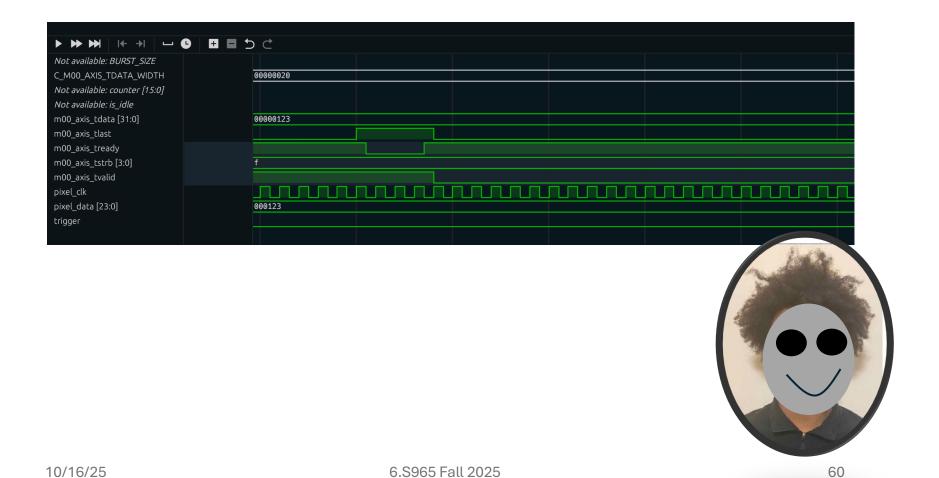

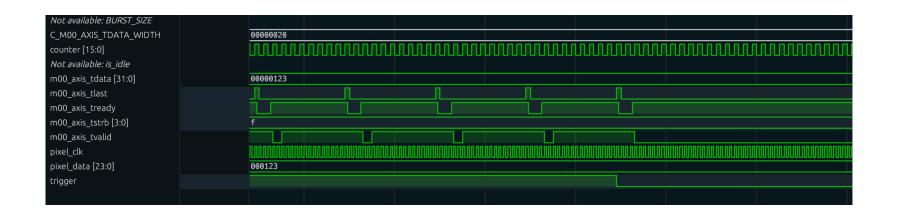

#### The TLAST Issue

I think in week 5, a decent number of you made data\_framers that failed at the end

I modified the S driver to deassert ready if last shows up

```

elif value.get("type") == "delay last read":

for i in range(value.get("duration",1)):

await falling_edge #wait until after a rising edge has passed.

if self.bus.axis tvalid.value == 1 and self.bus.axis tlast.value ==1:

self.bus.axis tready.value = 0 #set valid to be 1

await rising edge

await rising edge

await rising edge

await falling edge #wait until after a rising edge has passed

self.bus.axis tready.value = 1 #set valid to be 1

await read only

if self.bus.axis tvalid.value == 0: #ifnot there...

await RisingEdge(self.bus.axis_tvalid) #wait until it does go high

await rising edge

self.bus.axis tready.value = 1 #set valid to be 1

await read onlu

if self.bus.axis tvalid.value == 0: #ifnot there...

await RisingEdge(self.bus.axis_tvalid) #wait until it does go high

await rising edge

#self.bus.axis tready.value = 0 #set to 0 and be done.

```