# 6.S965 Digital Systems Laboratory II

Lecture 3:

More Simulation Thoughts

and

Zynq Architecture

#### Administrative

- Week 1's stuff due Friday at 5pm

- Week 2's stuff should be out at noon on Friday

- If you find yourself thinking, "I'm probably doing something stupid..." in the context of Vivado, the problem may not be you, it may be Vivado.

Please ask for help

# CocoTb Stuff

How some of it works...

# More on Cocotb and the Event Loop

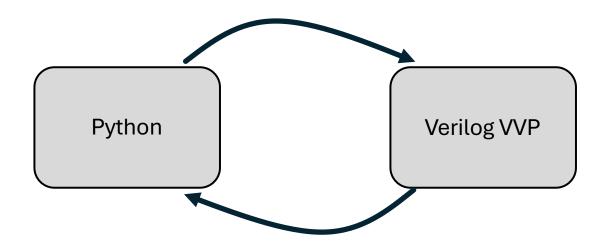

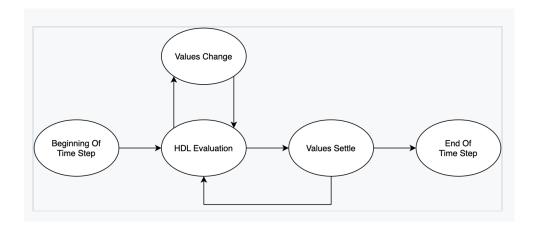

As we start to write more with Cocotb, we need to see what's going on with how it is interacting with the Verilog VPI/simulation cycle.

Understanding its underlying interactions with the Verilog simulations will help us write less problematic code.

## Verilog Simulation

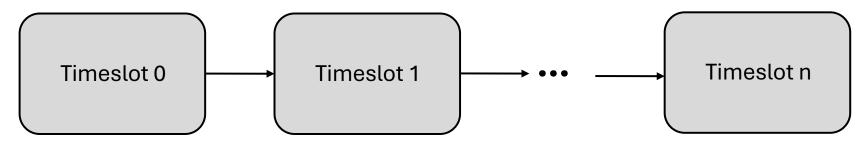

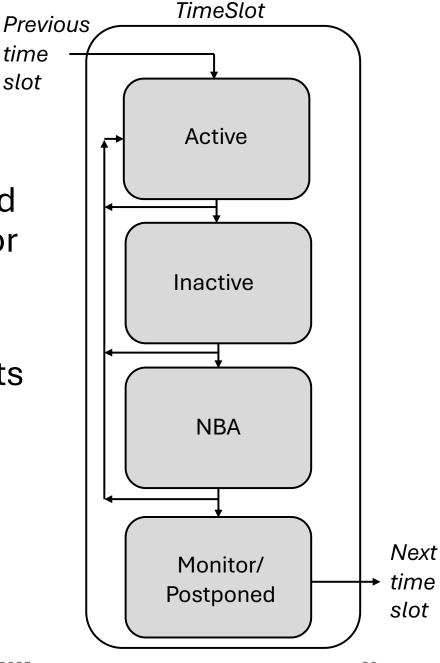

- A standard Verilog engine runs through a series of time slots.

- Within each time slot are regions in which different evaluations and updates are made

- The size of the simulation timeslot will be based off the timescale specified. For example:

- `timescale 1ns/1ps

- Means we have basically 1ps time step/slot size

<sup>&</sup>quot;Nonblocking Assignments in Verilog Synthesis, Coding Styles That Kill!" Clifford E. Cummings Sunburst Design, Inc.

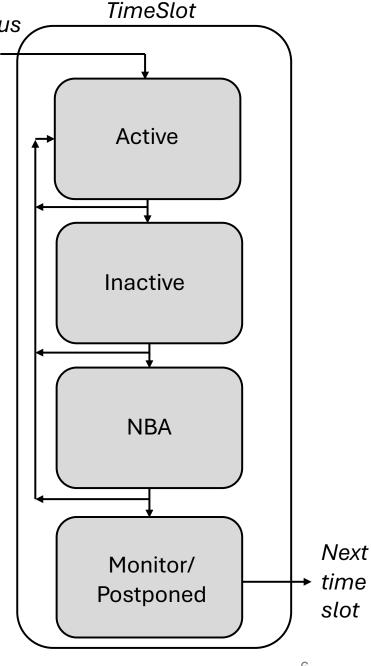

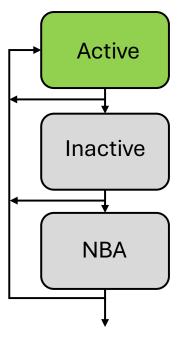

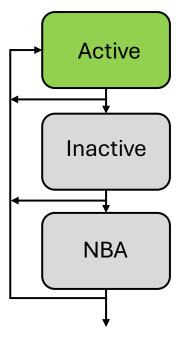

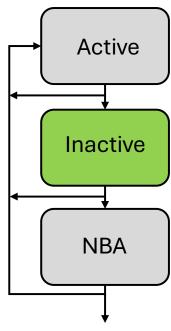

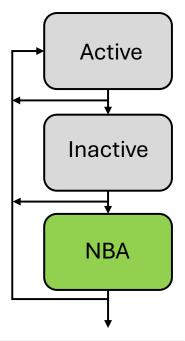

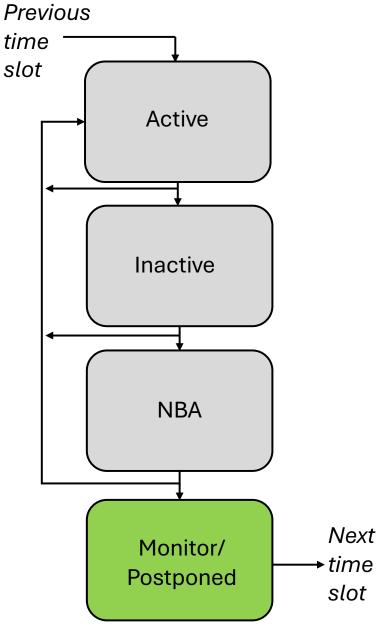

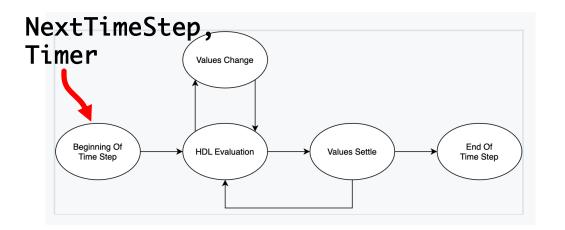

# Verilog Simulation Time Step

Previous time <del>|</del> slot

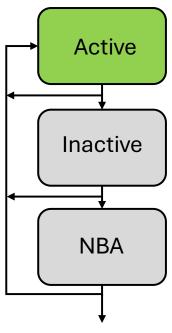

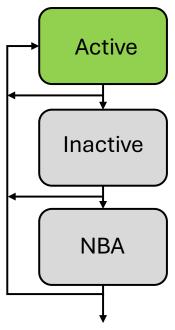

- Active:

- Blocking Assignments

- RHS of non-blocking assignments

- Continuous assignments

- Inactive Region:

- "#0 Blocking Assignments" (ignore)

- Non-Blocking Region:

- LHS updating of non-blocking assignments

- Monitor/Postponed Region:

- Meant for evaluation of results

#### Iterative Nature

- The simulation may do run through multiple cycles of the three big stages until things resolve

- Each iteration is a "deltacycle" or "delta-step"

- These are all zero-time events

time

slot

#### Example Code

- Here's some simple SystemVerilog:

- It has a variety of things being done here

- One a simulation step, all of the HDL is evaluated and processed in steps

```

logic clk;

logic [1:0] a,b,c,d,e;

assign a = b + c;

always_comb begin

b = c + d;

end

always_comb begin

d=e+2;

end

always_ff @(posedge clk)begin

c \le e+2:

end

```

#### **Active Region**

- Fully do (in any order) non-deterministic:

- assign a = b + c;

- b = c + d;

- d=e+2;

- Evaluate RHS of:

- c <= e+2;</li>

d updated and b updated. Because other lines use them in their RHS, the simulator will need to go back through again

```

logic clk;

logic [1:0] a,b,c,d,e;

assign a = b + c;

always_comb begin

b = c + d;

end

always_comb begin

d=e+2;

end

always_ff @(posedge clk)begin

c <= e+2;

end</pre>

```

#### **Active Region II**

- Redo (in any order) non-deterministic:

- assign a = b + c;

- b = c + d;

- Evaluate RHS of:

- c <= e+2;</li>

b updated. Depending on the order these lines were evaluated in, the first one might need to run again given the new value of <u>b</u>

```

logic clk;

logic [1:0] a,b,c,d,e;

assign a = b + c;

always_comb begin

b = c + d;

end

always_comb begin

d=e+2;

end

always_ff @(posedge clk)begin

c <= e+2;

end</pre>

```

## **Active Region III**

- Redo (in any order) non-deterministic:

- assign  $a = \underline{b} + c$ ;

- Evaluate RHS of:

- c <= e+2;</li>

Shouldn't be anything left dangling

```

logic clk;

logic [1:0] a,b,c,d,e;

assign a = b + c;

always_comb begin

b = c + d;

end

always_comb begin

d=e+2;

end

always_ff @(posedge clk)begin

c <= e+2;

end

```

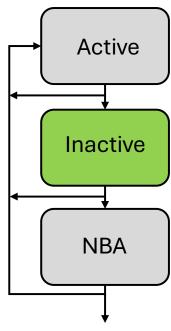

#### InActive Region

- Highly discourage to use this.

- Just skip this...is a weird delayed region that people use to force order on assignments

- Kinda like !important in CSS if anybody does webdev

```

logic clk;

logic [1:0] a,b,c,d,e;

assign a = b + c;

always_comb begin

b = c + d;

end

always_comb begin

d=e+2;

end

always_ff @(posedge clk)begin

c <= e+2;

end</pre>

```

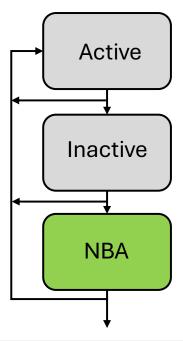

#### **NBA** Region

• Transfer result of e+2 to c

c updated. Because c was used in the assignments of b and a, we will return back to the Active region to recalculate

```

logic clk;

logic [1:0] a,b,c,d,e;

assign a = b + c;

always_comb begin

b = c + d;

end

always_comb begin

d=e+2;

end

always_ff @(posedge clk)begin

c <= e+2;

end

```

#### **Active Region IV**

- Fully do (in any order) non-deterministic:

- assign a = b + c;

- b = c + d;

b updated. Depending on the order these lines were evaluated in, the first one might need to run again given the new value of <u>b</u>

```

logic clk;

logic [1:0] a,b,c,d,e;

assign a = b + c;

always_comb begin

b = c + d;

end

always_comb begin

d=e+2;

end

always_ff @(posedge clk)begin

c <= e+2;

end

```

#### Active Region V

- Redo (in any order) non-deterministic:

- assign  $a = \underline{b} + c$ ;

- Evaluate RHS of:

- c <= e+2;</li>

Shouldn't be anything left dangling

```

logic clk;

logic [1:0] a,b,c,d,e;

assign a = b + c;

always_comb begin

b = c + d;

end

always_comb begin

d=e+2;

end

always_ff @(posedge clk)begin

c <= e+2;

end

```

## InActive Region II

- Highly discourage to use this.

- Just skip this...is a weird delayed region that people use to force order on assignments

- Kinda like !important in CSS if anybody does webdev

```

logic clk;

logic [1:0] a,b,c,d,e;

assign a = b + c;

always_comb begin

b = c + d;

end

always_comb begin

d=e+2;

end

always_ff @(posedge clk)begin

c <= e+2;

end</pre>

```

## **NBA** Region II

Nothing new this time through

```

logic clk;

logic [1:0] a,b,c,d,e;

assign a = b + c;

always_comb begin

b = c + d;

end

always_comb begin

d=e+2;

end

always_ff @(posedge clk)begin

c <= e+2;

end

```

## **Monitor Region**

Only after we've completely "stabilized" in all of our calculations.

\*NBA = Non-blocking Assignments

It is absolutely possible to have unsolveable Verilog

A simple combinational loop is technically infinite:

```

logic [7:0] d;

assign d = d + 1;

```

- Might get some warnings about combinational loop

- In simulation iVerilog will just say this is always X

# Would you ever run through NBA more than twice?

- In the earlier "good" example we ran through the NBA region twice:

- First time through it we did a LHS update...this triggered a loopback since some continual assignments used the thing updated in their RHS

- Second time through nothing was left to do.

- Once a non-blocking assignment is carried out, it is removed from the list of things that needs to be addressed (prevents it from being done multiple times...)

- So question: Could you ever run through the NBA more than twice on a time step?

#### Some messed up Verilog:

```

module messed_up(

input wire clk,

input wire rst,

input wire en,

output logic [7:0] count

logic a,b,c;

initial begin

//way to say these values start at something rather than X

a = 0;

b = 0;

c = 0;

count = 0;

end

always ff @(posedge en)begin

count <= count +1;</pre>

a <= ~a:

end

always_ff @(posedge a)begin

count <= count+1;</pre>

b <= ~b:

end

always ff @(posedge b) begin

count <= count + 1;</pre>

c <= ~c;

end

endmodule

```

#### Wrote this Test Script:

```

@cocotb.test()

async def test a(dut):

"""cocotb test for seven segment controller"""

dut. log.info("Starting...")

cocotb.start soon(Clock(dut.clk, 10, units="ns").start(start high=False))

dut.en.value = 0;

dut.rst.value = 1:

await Timer(10, "ns")

dut.rst.value = 0;

dut. log.info(f"About to set en to 1.")

dut.en.value = 1:

await RisingEdge(dut.en)

dut. log.info(f"Rising Edge of en caught!")

dut._log.info(f" Values: en: {dut.en.value}, a: {dut.a.value}, b: {dut.b.value}")

await RisingEdge(dut.a)

dut. log.info(f"Rising Edge of a caught!")

dut._log.info(f" Values: en: {dut.en.value}, a: {dut.a.value}, b: {dut.b.value}")

await RisingEdge(dut.b)

dut. log.info(f"Rising Edge of b caught!")

dut. log.info(f" Values: en: {dut.en.value}, a: {dut.a.value}, b: {dut.b.value}")

await Timer(99, "ns")

```

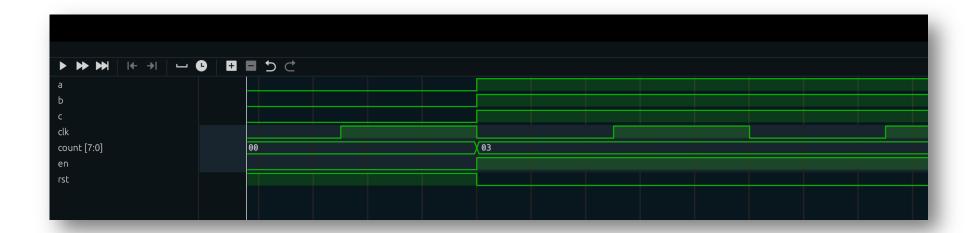

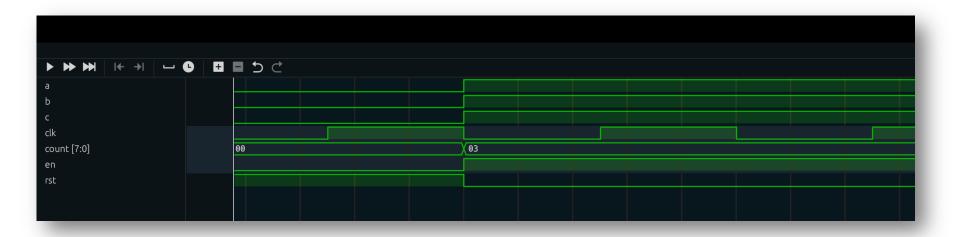

#### When Run

- en goes high...

- count goes from 00 to 03 instantaneously at 10ns...

#### With Readout...

```

10.00ns INFO

cocotb.messed_up

About to set en to 1.

10.00ns INFO

cocotb.messed_up

Rising Edge of en caught!

10.00ns INFO

cocotb.messed_up

Values: en: 1, a: 0, b: 0

cocotb.messed_up

Rising Edge of a caught!

10.00ns INFO

Values: en: 1, a: 1, b: 0

10.00ns INFO

cocotb.messed_up

10.00ns INFO

Rising Edge of b caught!

cocotb.messed_up

10.00ns INFO

cocotb.messed_up

Values: en: 1, a: 1, b: 1

```

```

10.00ns INFO

cocotb.messed_up

About to set en to 1.

10.00ns INFO

cocotb.messed up

Rising Edge of en caught!

10.00ns INFO

Values: en: 1, a: 0, b: 0

cocotb.messed_up

10.00ns INFO

cocotb.messed_up

Rising Edge of a caught!

10.00ns INFO

Values: en: 1, a: 1, b: 0

cocotb.messed_up

10.00ns INFO

Rising Edge of b caught!

cocotb.messed_up

10.00ns INFO

cocotb.messed_up

Values: en: 1, a: 1, b: 1

```

- For several cycles there the delta steps finish and then the NBA is applied. That RHS assignment is to a value in the sensitivity list of a always\_ff, bringing its lines of stuff onto the "queue" of stuff to evaluate. Forcing another full round (at least)

- Notice how the the timestamp of all of this is exactly the same!

- This is all happening in zero-time as the simulator resolves itself.

- So it went through NBA like four/five times

## Could You Mess This Really Up?

Oh yeah...

This runs fine but...

```

module messed_up(

input wire clk,

input wire rst,

input wire en,

output logic [7:0] count

logic a,b,c;

initial begin

//start at something rather than X

a = 0;

b = 0;

c = 0;

count = 0;

end

always_ff @(posedge en, posedge c)begin

count <= count +1;</pre>

a <= ~a:

end

always_ff @(posedge a, negedge a)begin

count <= count+1;</pre>

b <= ~b:

end

always ff @(posedge b,negedge b) begin

count <= count + 1;</pre>

c <= ~c:

end

endmodule

```

## Could You Really Mess This Up?

Hard Crash!

Gets stuck in a death spiral it never gets out of

```

module messed_up(

input wire clk,

input wire rst,

input wire en,

output logic [7:0] count

logic a,b,c;

initial begin

//start at something rather than X

a = 0;

b = 0:

c = 0;

count = 0;

end

always_ff @(posedge en, posedge c, negedge c)begin

count <= count +1;</pre>

a <= ~a:

end

always ff @(posedge a, negedge a)begin

count <= count+1;</pre>

b <= ~b:

end

always ff @(posedge b,negedge b) begin

count <= count + 1;</pre>

c <= ~c:

end

endmodule

```

#### Conclusion

- You can break the simulator in many different ways.

- Thankfully if you write good HDL, it minimizes the chances of that.

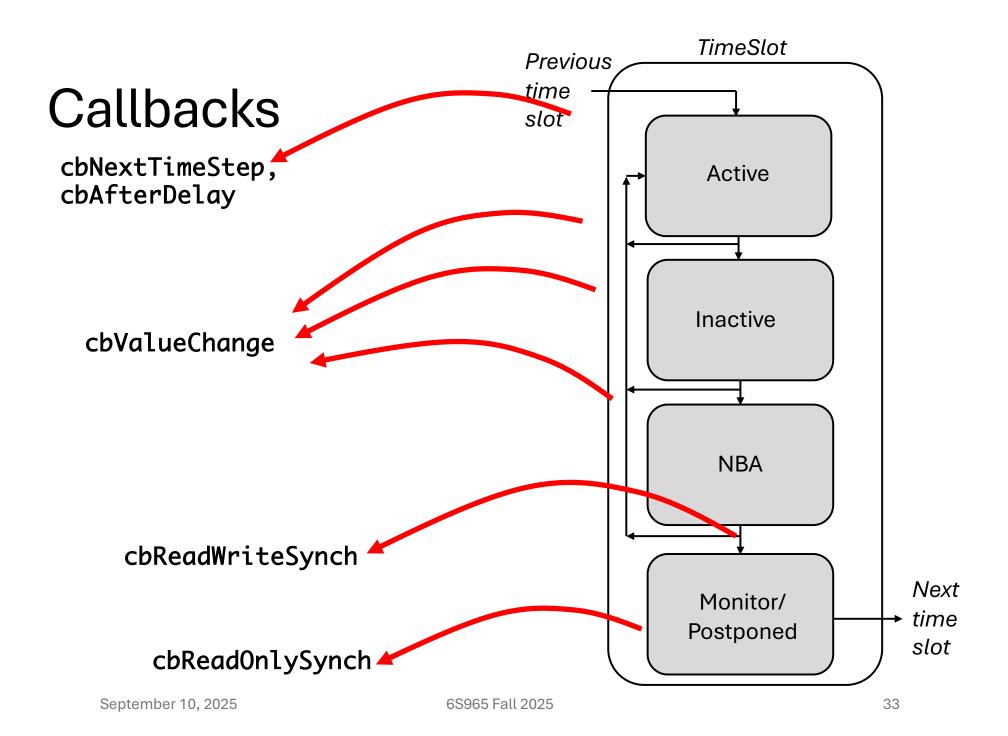

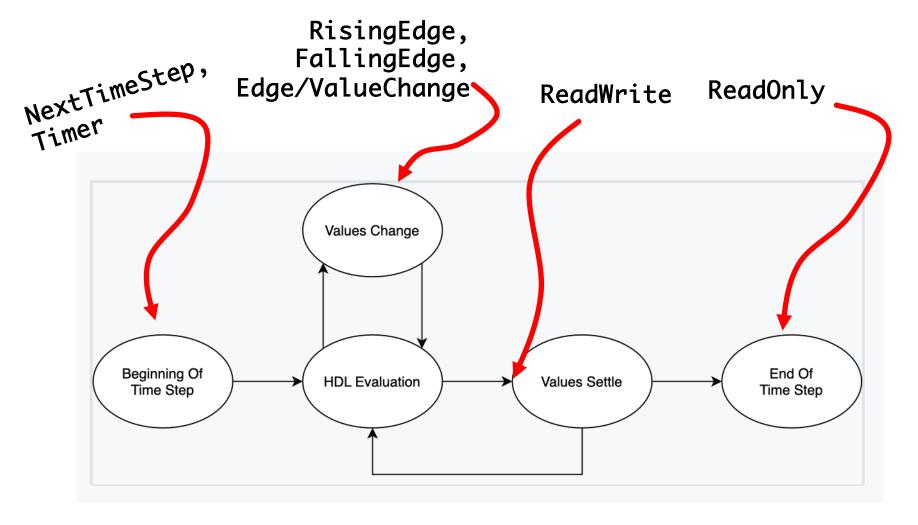

# So How Does CocoTB interact with Verilog?

- It is interesting.

- You have two separate programs running and they are effectively ping-ponging control back and forth between each other.

#### PLI/VPI Usage

- time slot

- You use PLI/VPI to run and interact with the simulator

- And you also set up callbacks to pause the simulator at various points to allow you to check in

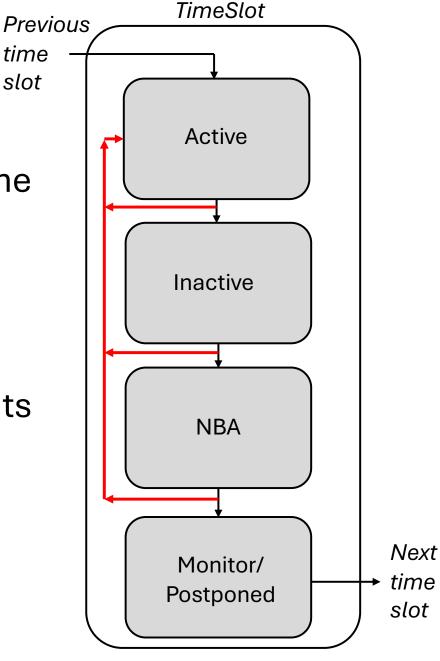

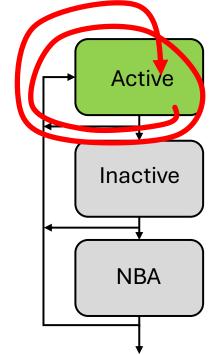

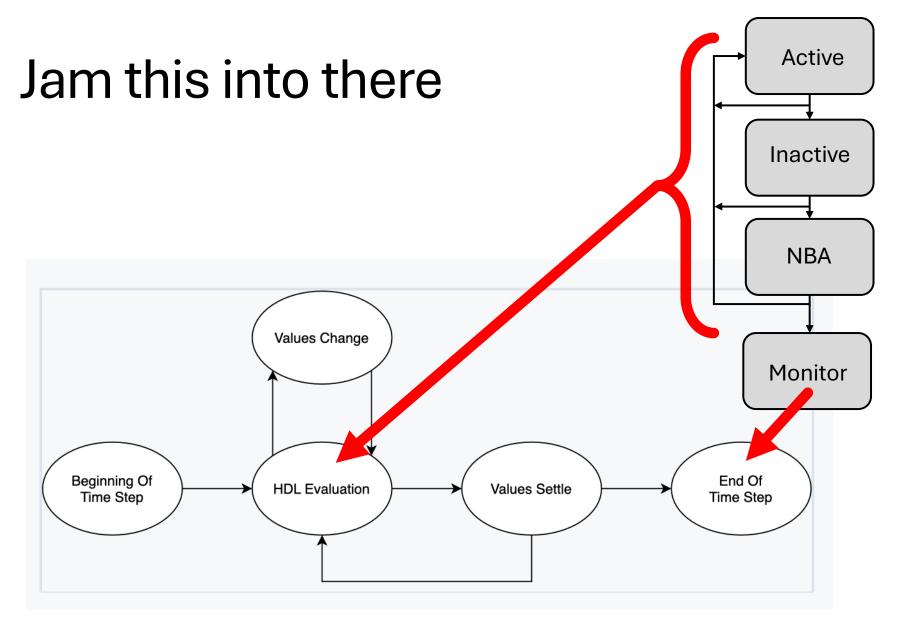

#### **Previous** time slot Verilog VPI **Active** As far as where it gets its hooks into the simulation, it has several Inactive major callbacks to different points in simulation: others **NBA** readonly Next Monitor/ **>** time Postponed slot

#### Some Common VPI Callbacks

- Taken from cocotb source code

- Also refer to icarusVeril og source code

```

CALLBACK REASONS **********

Simulation related ********

#define cbValueChange

#define cbStmt

#define cbForce

#define cbRelease

********** Time related ******************/

5

#define cbAtStartOfSimTime

#define cbReadWriteSynch

#define cbReadOnlySynch

#define cbNextSimTime

#define cbAfterDelay

Action related ****************/

#define cbEndOfCompile

10

#define cbStartOfSimulation

11

#define cbEndOfSimulation

12

#define cbError

13

#define cbTchkViolation

14

#define cbStartOfSave

15

#define cbEndOfSave

16

#define cbStartOfRestart

17

#define cbEndOfRestart

18

#define cbStartOfReset

19

#define cbEndOfReset

#define cbEnterInteractive

#define cbExitInteractive

#define cbInteractiveScopeChange 23

#define cbUnresolvedSystf

24

```

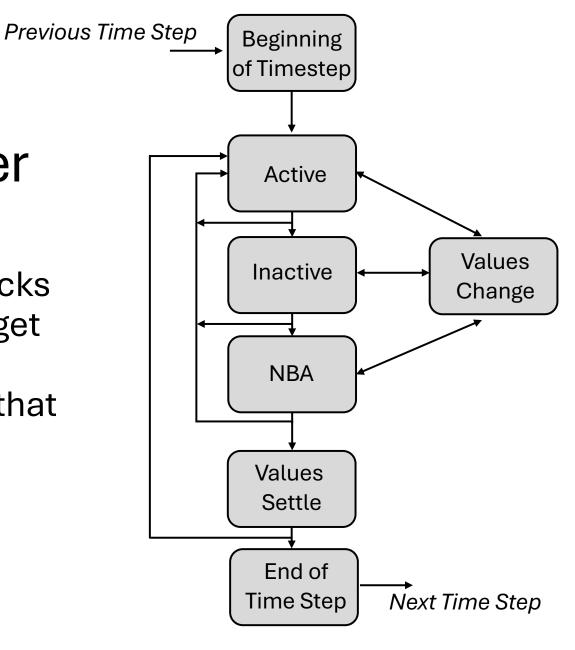

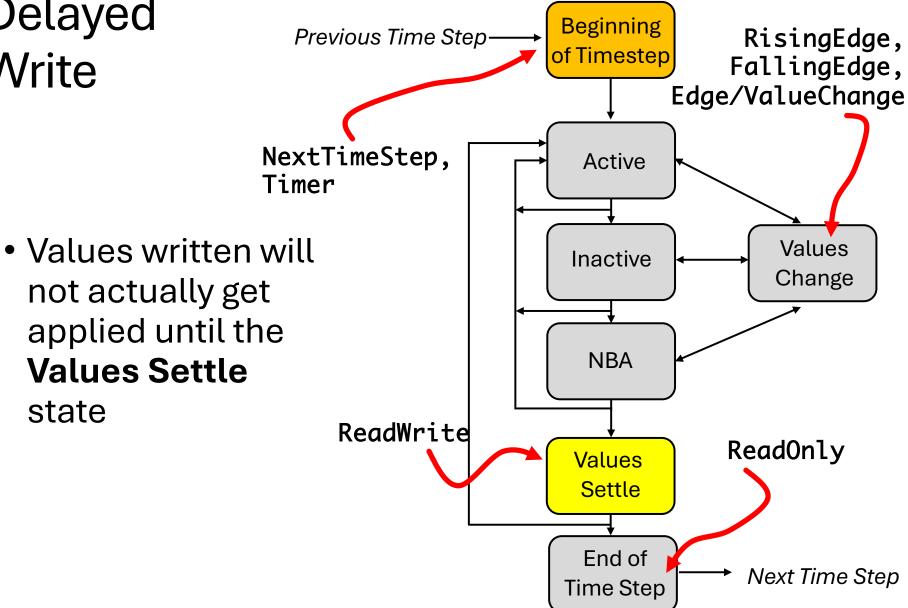

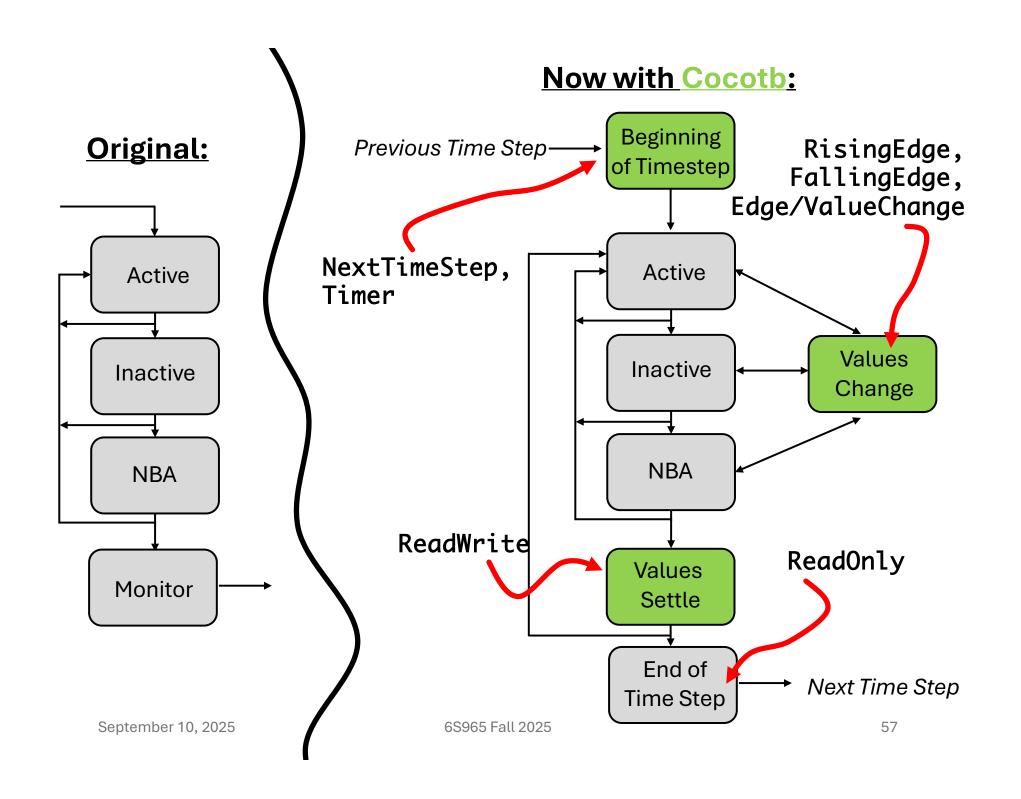

## CocoTb's Official<sup>TM</sup> Timing Model

Cocotb uses these callbacks to integrate a layer of control around the standard Verilog Simulation Construct

The Result is their Own Simulation/Timing Model

https://github.com/cocotb/cocotb/blob/master/docs/source/timing\_model.rst

https://github.com/cocotb/cocotb/blob/master/docs/source/timing\_model.rst

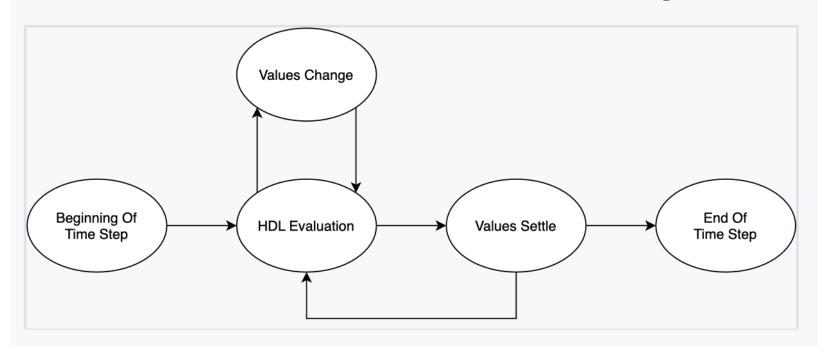

# Drawing the Previous Two previous slides together

Using VPI callbacks and Python you get this hybrid simulation step that runs

# So in CocoTb when you want to set a Callback...

- You're going to do that through issuing await

- In Cocotb when you issue an await, what you're doing is throwing control to the underlying Verilog simulator and it will then return control back to you when it hits that event and the await returns

#### List of Events to await for

- NextTimeStep

- Timer

- RisingEdge, FallingEdge, Edge (soon to be ValueChange)

- ReadWrite

- ReadOnly

- These all have almost 1:1 mappings to VPI callbacks

### CocoTb's Timing Model

https://github.com/cocotb/cocotb/blob/master/docs/source/timing\_model.rst

# Beginning of TimeStep

- Start of a step.

- You get here by awaiting a Timer or awaiting the NextTimeStep the simulator encounters!

- You can Read or Write values here.

- When await Timer(10, "ns") returns, you're in the beginning of the timestep.

#### All Value Assignments in Cocotb

- All Value Assignments made through Cocotb are non-blocking and do not apply immediately!

- Run this code:

```

await Timer(10, "ns") #in start of timestep:

dut._log.info(f"clk: {dut.clk.value} en:{dut.en.value} count: {dut.count.value.integer}")

dut.en.value = 1 #set en to be 1...now check its value...

dut._log.info(f"clk: {dut.clk.value} en:{dut.en.value} count: {dut.count.value.integer}")

```

#### • Will return this:

```

20.00ns INFO cocotb.simple_logic2 clk: 1 en:0 count: 0 clk: 1 en:0 count: 0

```

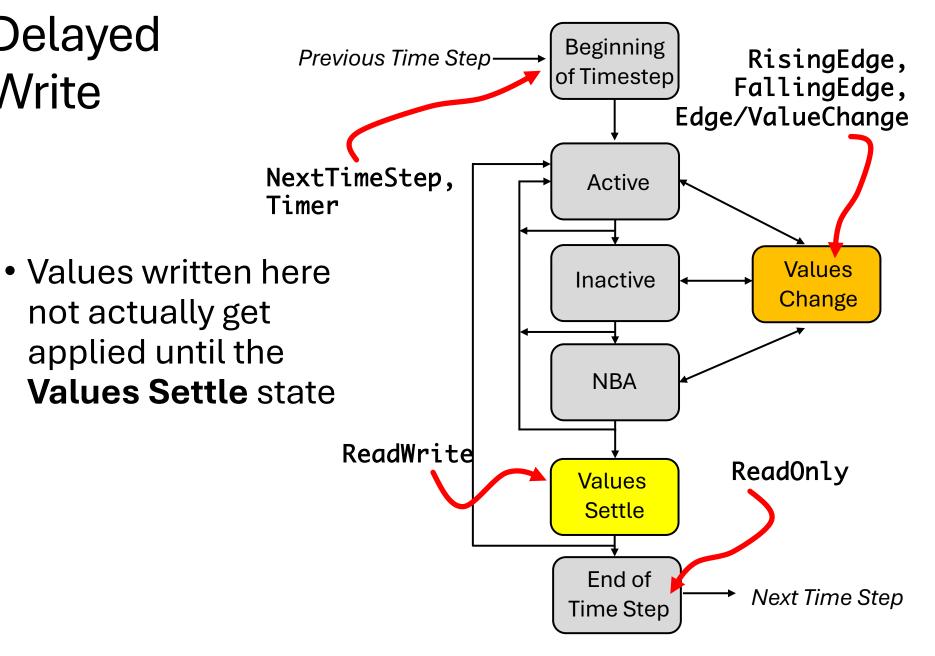

#### Delayed Write

**Values Settle**

state

#### One Exception

• In simulation states where you can write the following will get queued up:

```

dut.some_signal.value = 1

```

However, you can override this and set immediately:

```

dut.some_signal.setimmediatevalue(1)

```

- This will immediately change the value in the simulation.

- Be very very careful...only useful for initial conditions (maybe)...can cause race conditions and/or nondeterminism

#### All Value Assignments in Cocotb

If I change that code from the previous page:

```

await Timer(10, "ns") #in start of timestep:

dut._log.info(f"clk: {dut.clk.value} en:{dut.en.value} count: {dut.count.value.integer}")

dut.en.setimmediatevalue(1) #set en to be 1...now check its value...

dut._log.info(f"clk: {dut.clk.value} en:{dut.en.value} count: {dut.count.value.integer}")

```

#### Will return this:

```

20.00ns INFO cocotb.simple_local clk: 1 en:0 count: 0 clk: 1 en:1 count: 0

```

JK it didn't do this.

the simulation hangs forever and I'm not sure why.

Must have introduced a race condition junno

September 10, 2025 6S965 Fall 2025 45

## NextTimeStep()!

- It will not just jump 1ns or 1ps forward

- SystemVerilog/Verilog are not simulating useless time in between events. There is a schedule of events and it will jump to the next even that is scheduled to happen.

- In many clocked systems (in simulation), after everything has settled on the rising edge of a clock, the next even will likely be the falling edge.

#### When Done with Beginning...

Move on...can never go back (within this timestep)

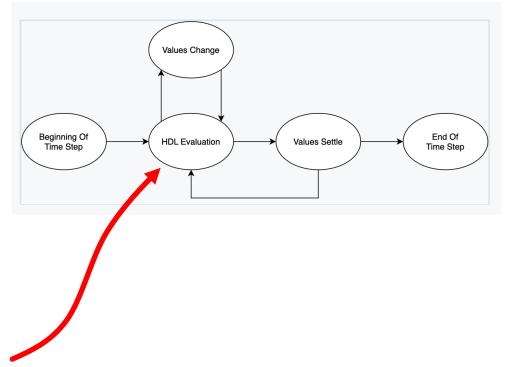

# HDL Evaluation Step

- No way to get direct insight into the progress of the HDL evaluation (vvp engine). That will run until resolved and values settle...

- Or until it encounters a change callback

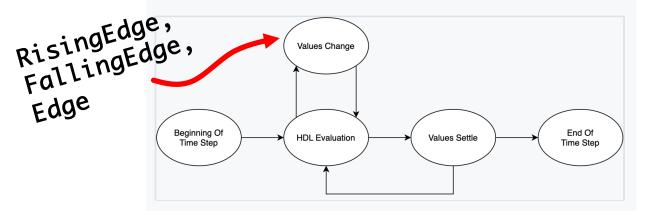

#### Changes

- During HDL Evaluation if a signal with a callback on it changes appropriately, the callback fires and control returns to Cocotb/Python

- You can do RisingEdge, FallingEdge, and Edge

- Edge will be renamed ValueChange in Cocotb 2.0

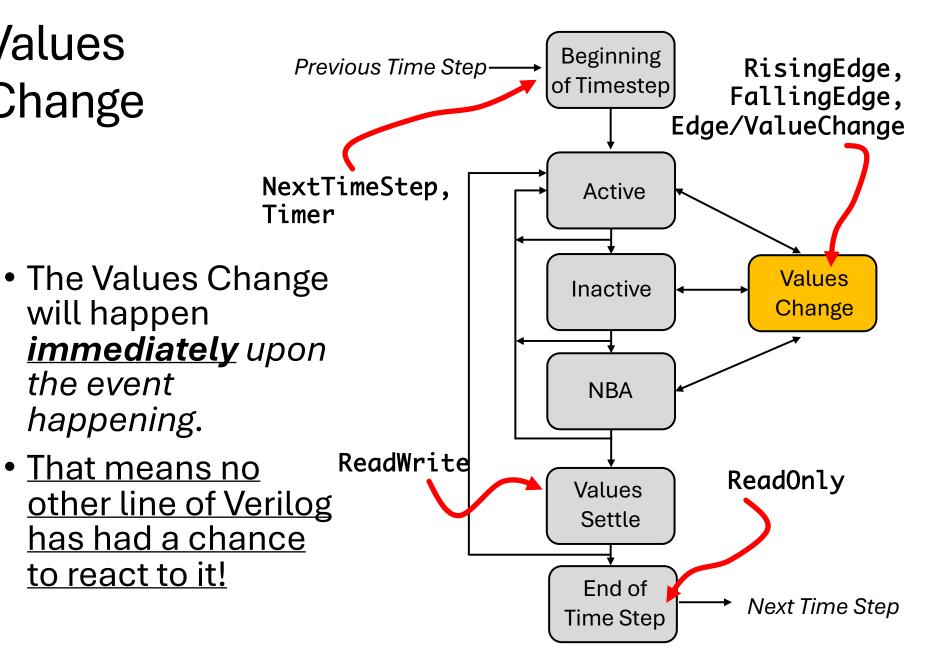

### Values Change

the event

happening.

## Value Change

- You can <u>read</u> and <u>write</u> signals in the Values Change state.

- However, the state of values may be nondeterministic here.

- BUT what you read here was unaffected by whatever change brought you in...

#### Delayed Write

#### Delta Steps Happen

- When HDL Evaluation is done and no more Values Change, simulation is stable.

- Moves to Values Settle

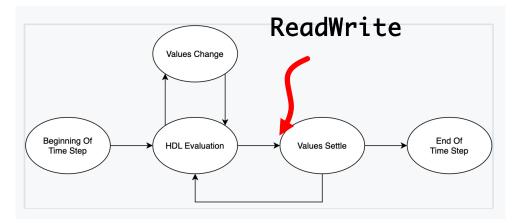

#### Values Settle

- awaiting ReadWrite puts you in this point of your simulation and pauses things.

- Everything, including non-blocking assignments internal to the DUT will have resolved.

- External signals (<u>specified from Cocotb</u>) will not have been applied yet!

- You can read/write values here.

- Reads are stable

- Writes after you're done here and sim moves on.

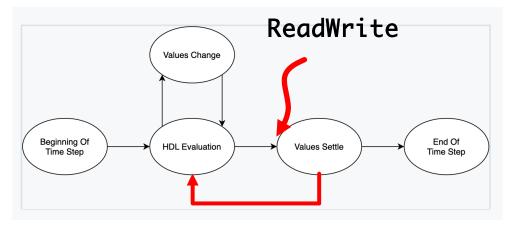

#### Values Settle

- You can read/write values

- When the simulator continues, those delayed writes from Cocotb will be applied

- The Verilog simulator will determine if it needs to revisit the HDL evaluation stage

- If not, it goes to EndofTimeStep

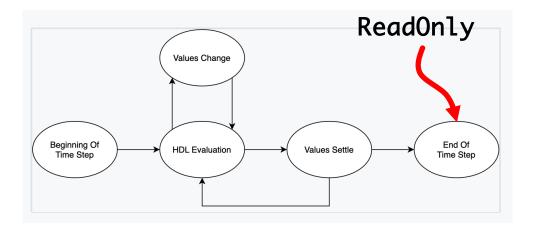

#### EndOfTimeStep

- Effectively the original Monitor Phase

- This is the only state/phase where you can only Read signals. Writing is not allowed since you have already passed the spot in the timestep where you can apply external signals (Values Settle)

- Can't go back.

- await ReadOnly() gets you here.

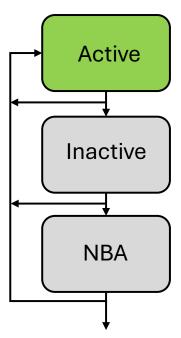

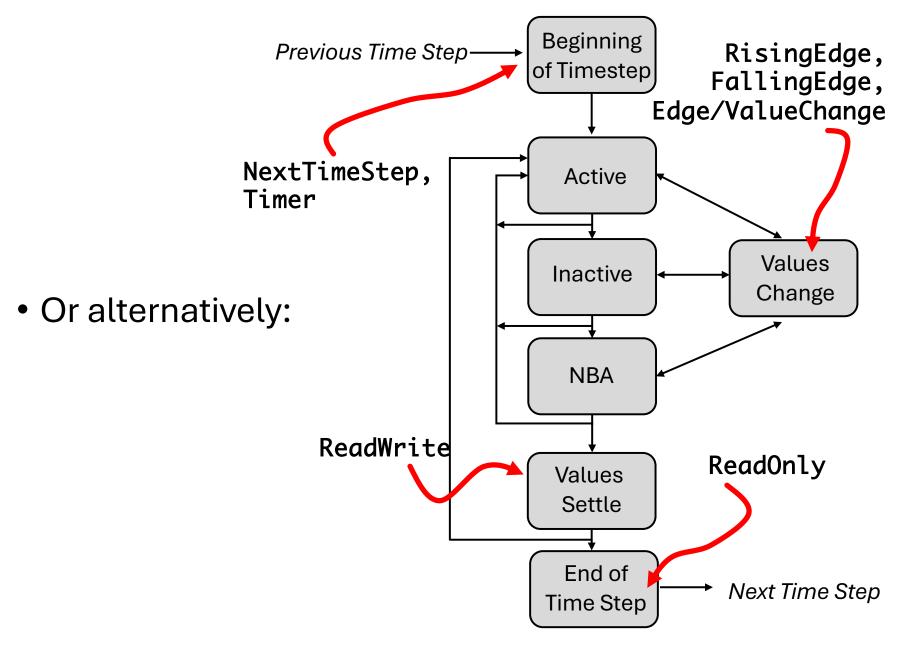

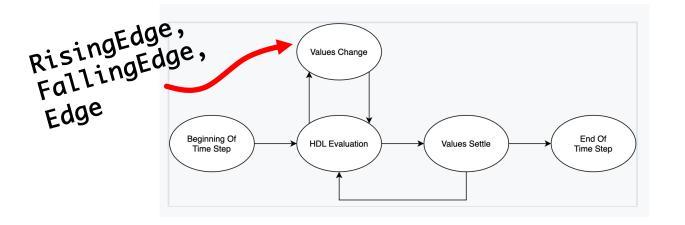

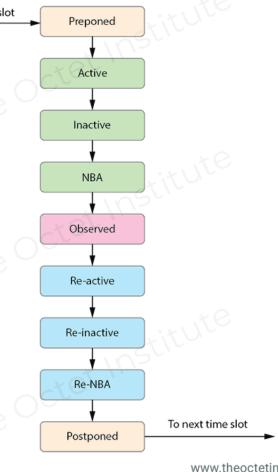

### Cocotb and SystemVerilog

Simplified SV time step (loopbacks not shown)

- Both simulation structures From previous time slot

have tried to achieve the

same thing and added on

many of the same structures

- Clearly broken out region to react and inject external inputs to DUT

- Clear Begin/End Spots

www.theoctetinstitute.com

#### Cocotb 2.0 Updates

- The Naming and Everything is Very Confusing

- Cocotb 2.0 is making an effort to:

- Have the current step of a simulation be more transparent

- Have the naming be more clear

- We'll see how that evolves in coming months/years

#### Maybe Cocotb Demo

Try to walk through the simulation trying to mess with it.