## 6.S965 Digital Systems Laboratory II

Lecture 12

#### Administrative

- Last Lecture

- Finish Week 6's material (the RFSoC stuff) by Friday please.

- Then projects (we'll be having meetings)

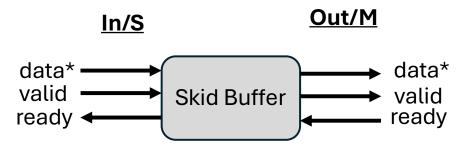

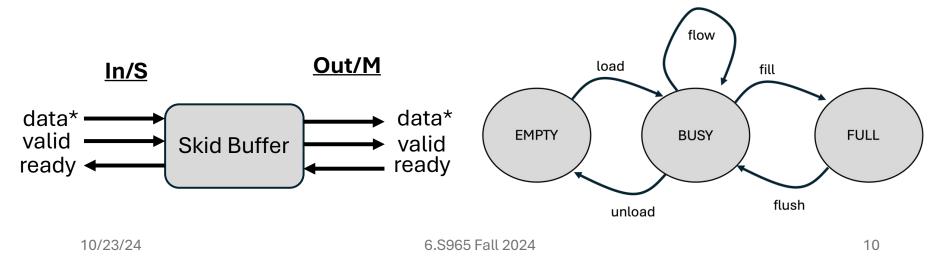

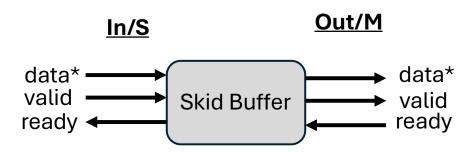

- Wrote a skid buffer and then were trying to test it with a variety of inputs,

- But also get a sense of how well we were testing it

### **Cocotb Coverage**

- Cocotb variant Library

- Provides some structure and tracking for coverage

| cocotb_coverage 1.0 documentat                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ion » Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| O C Constrained Random Verification Features in Constrained Random Verification Constrained Random Verification Features in Constrained Random Verifi | Introduction         Functional Coverage in SystemVerilog         In SystemVerilog a fundamental coverage unit is a coverpoint. It contains several bins and each bin may contain several values. Every coverpoint is associated with a variable or signal. At sampling event, the coverpoint variable value is compared with each defined bin. If there is a match, then the number of hits of the particular bin is incremented. Coverpoints are organized in covergroups, which are specific class-like structures. A single covergroup may have several instances and each instance may collect coverage independently. A covergroup requires sampling, which may be defined as a logic event (e.g. a positive clock edge). Sampling may also be called implicitly in the testbench procedural code by invoking a sample() method of the covergroup instance. A bin may be also defined as an ignore_bins, which means its match does not increase a coverage count, or an illegal_bins, which results in error when hit during the test execution.         Another coverage construct in SystemVerilog is a cross. It automatically generates a Cartesian product of bins from several covergoints. It is a useful feature simplifying the functional coverage generation. As it may be difficult or unnecessary to cover all the cross-bins, some of them may be excluded from the analysis. This is possible using the bins d intersect syntax.         The most important limitations of the SystemVerilog functional coverage features are:         • straightforward bins matching oriteria – only satisfied by equality or inclusion relation;         • bins may be only constants or transitions (possibly wildcard);         • lat coverage structure – cover groups cannot contain other cover groups, which would correspond better to a verification plan scheme);    < |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | not possible to get the detailed coverage information in real time (e.g. when a specific bin was hit).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Functional Coverage with cocotb-coverage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | The general assumptions for the architecture of the functional coverage features are as follows: <ul> <li>functional coverage structure should better match a real verification plan;</li> <li>its syntax should be more flexible, but a separation between coverage and executable code should be maintained;</li> <li>features for analysing the coverage during test execution should be added or extended;</li> <li>coverage primitives should be able to monitor testbench objects at a higher level of abstraction.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | The implemented mechanism is based on the idea of decorator design pattern. In Python, a decorator syntax is                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

CoverPoint and CoverCross and Cover... Group/Section

- We started to classify existence into various bins of coverage. Each dimension was called a Coverpoint

- We started to lump them together.

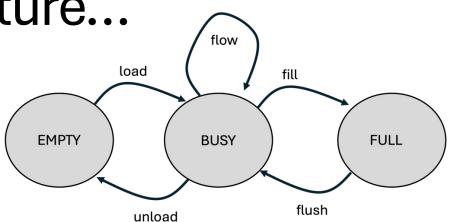

- We at first looked at how well we were testing the FSM portion of the skid buffer and its state transitions

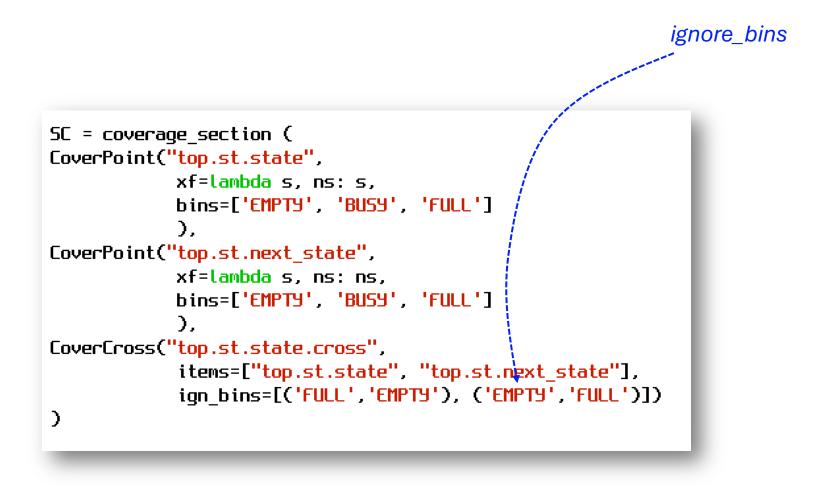

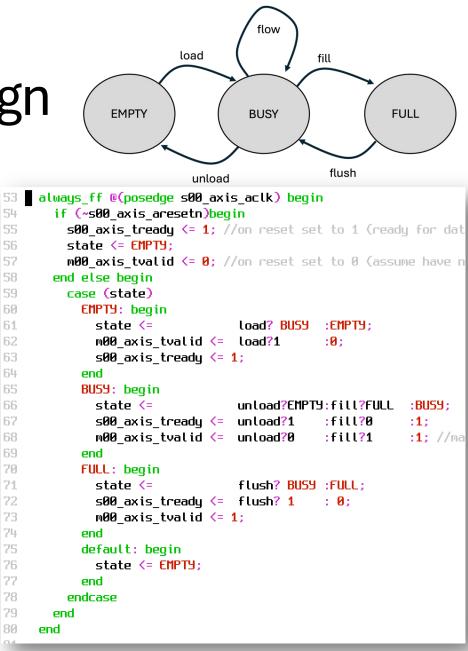

### If you know things shouldn't happen

#### Can now target 100% coverage

If you can prove through some nice mechanism or another which bins should be reachable and which are false or unachievable, then you can view your coverage more as a milestone

> top.st : <cocotb coverage.coverage.CoverItem object at 0x105f2a260>, coverage=13, size=13 top.st.next state : <cocotb coverage.coverage.CoverPoint object at 0x106885500>, coverage=3, size=3 BIN EMPTY : 9365 BIN BUSY : 307 BIN FULL : 328 top.st.state : <cocotb coverage.coverage.CoverPoint object at 0x105f2a230>, coverage=10, size=10 BIN EMPTY : 9365 BIN BUSY : 307 BIN FULL : 328 top.st.state.cross : <cocotb\_coverage.coverage.CoverCross object at 0x106885690>, coverage=7, size=7 BIN ('EMPTY', 'EMPTY') : 9343 BIN ('EMPTY', 'BUSY') : 22 BIN ('BUSY', 'EMPTY') : 22 BIN ('BUSY', 'BUSY') : 247 BIN ('BUSY', 'FULL') : 38 BIN ('FULL', 'BUSY') : 38 BIN ('FULL', 'FULL') : 290

Different tests but still you can see we got 100% coverage

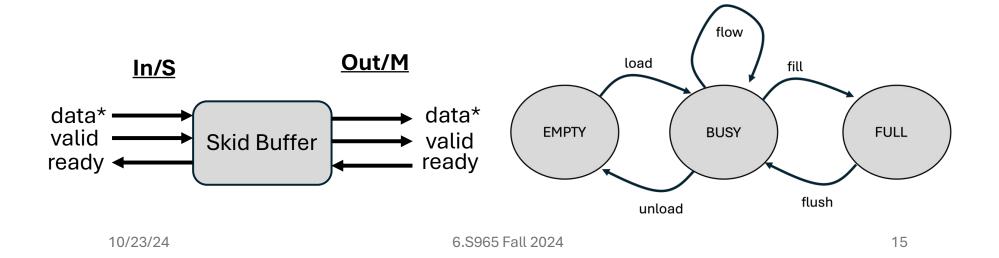

#### Further Pushing on this System

This simple FSM description...glossed over the potential complexity of the implementation: 3 states, each connected to 2 signals (valid/ready) per interface, for a total of 16 possible transitions out of each state, or 48 possible state transitions total.

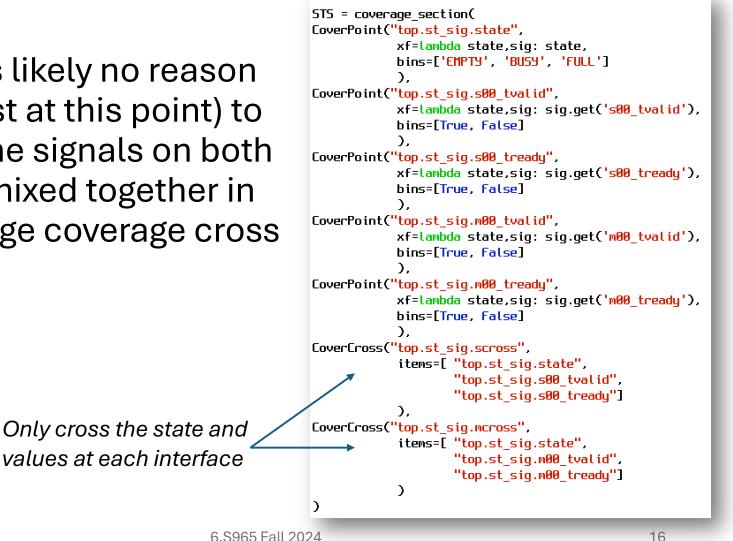

#### So let's do state and input

- Come up with STS covergroup (State and Signals)

- I want to look at the different states of my module as well as its exposure to different signal combinations on both S00 and M00 side

```

STS = coverage section(

CoverPoint("top.st sig.state",

xf=lambda state,sig: state,

bins=['EMPT9', 'BUS9', 'FULL']

).

CoverPoint("top.st sig.s00 tvalid",

xf=lambda state,sig: sig.get('s00 tvalid'),

bins=[True, False]

).

CoverPoint("top.st sig.s00 tready",

xf=lambda state,sig: sig.get('s00 tready'),

bins=[True, False]

).

CoverPoint("top.st sig.m00 tvalid",

xf=lambda state,sig: sig.get('m00 tvalid'),

bins=[True, False]

),

CoverPoint("top.st sig.m00 tready",

xf=lambda state,sig: sig.get('m00 tready'),

bins=[True, False]

).

CoverCross("top.st sig.cross",

items=[ "top.st sig.state",

"top.st sig.s00 tvalid".

"top.st sig.s00 tready".

"top.st sig.m00 tvalid".

"top.st sig.m00 tready"]

)

)

```

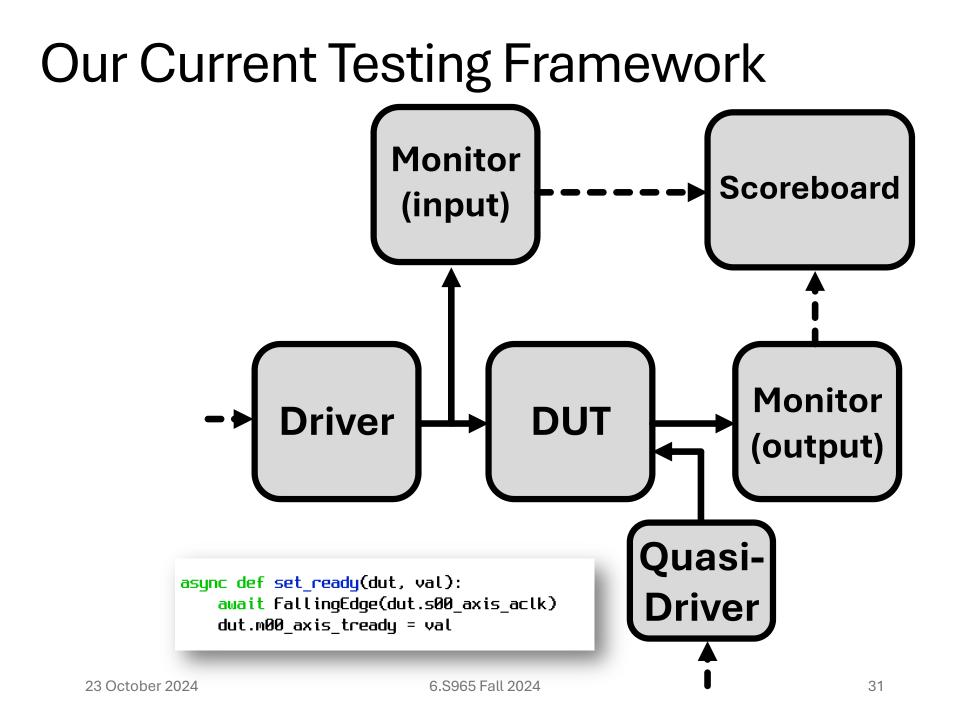

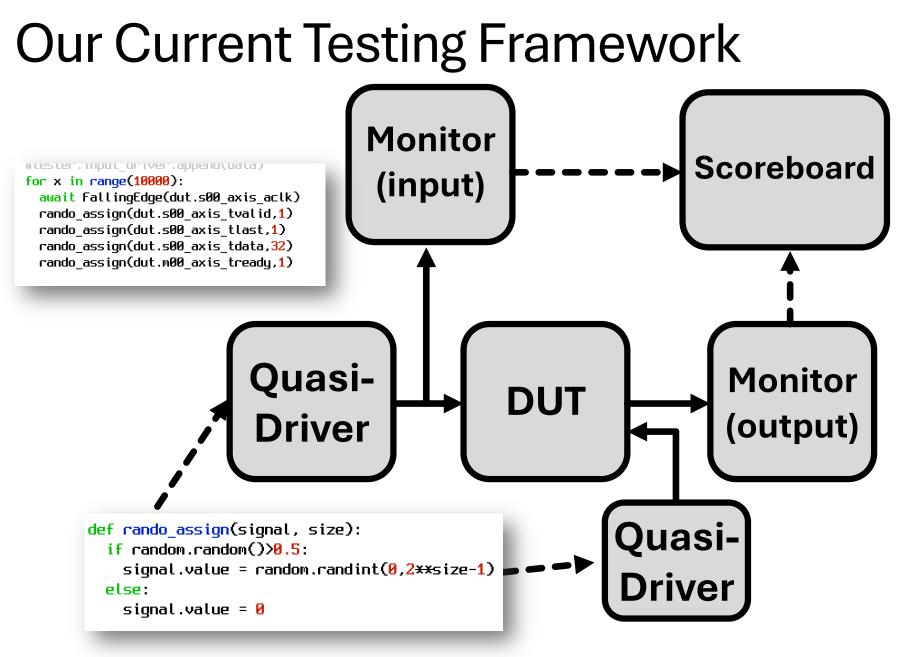

### Just Start Throwing Stuff at it...

Depart for a moment and just start using random numbers to set values on these four lines and see what patterns emerge

```

def rando_assign(signal, size):

if random.random()>0.5:

signal.value = random.randint(0,2**size-1)

else:

signal.value = 0

```

```

for x in range(1000):

await FallingEdge(dut.s00_axis_aclk)

```

rando\_assign(dut.s00\_axis\_tvalid,1)

rando\_assign(dut.s00\_axis\_tlast,1)

rando\_assign(dut.s00\_axis\_tdata,32)

rando\_assign(dut.m00\_axis\_tready,1)

## **Resulting Waveform**

| C_M00_AXIS_TDATA_WIDTH | 00000020                                                                                              |

|------------------------|-------------------------------------------------------------------------------------------------------|

| C_S00_AXIS_TDATA_WIDTH | 00000020                                                                                              |

| data_buffer_wren       |                                                                                                       |

| data_out_wren          |                                                                                                       |

| fill                   |                                                                                                       |

| flow                   |                                                                                                       |

| flush                  |                                                                                                       |

| insert                 |                                                                                                       |

| load                   |                                                                                                       |

| remove                 |                                                                                                       |

| m00_axis_aclk          |                                                                                                       |

| m00_axis_aresetn       |                                                                                                       |

| m00_axis_tdata [31:0]  |                                                                                                       |

| m00_axis_tlast         |                                                                                                       |

| m00_axis_tvalid        | ע ערביים באריינים איני איני איני איני איני איני איני                                                  |

| m00_axis_tready        |                                                                                                       |

| m00_axis_tstrb [3:0]   |                                                                                                       |

| s00_axis_aclk          |                                                                                                       |

| s00_axis_aresetn       |                                                                                                       |

| s00_axis_tdata [31:0]  |                                                                                                       |

| s00_axis_tvalid        |                                                                                                       |

| s00_axis_tready        | ביין היה הדיין ווידין המוכידה בממורה וראלי המוכידה במורה או המוכידה המוכידה היה הדיין היה הדיין היה ה |

| state [31:0]           |                                                                                                       |

| s00_axis_tlast         |                                                                                                       |

| s00_axis_tstrb [3:0]   |                                                                                                       |

| tdata_buffer [31:0]    |                                                                                                       |

| tlast_buffer           |                                                                                                       |

| tstrb_buffer [3:0]     |                                                                                                       |

| unload                 |                                                                                                       |

| use_buffered_data      |                                                                                                       |

|                        |                                                                                                       |

|                        |                                                                                                       |

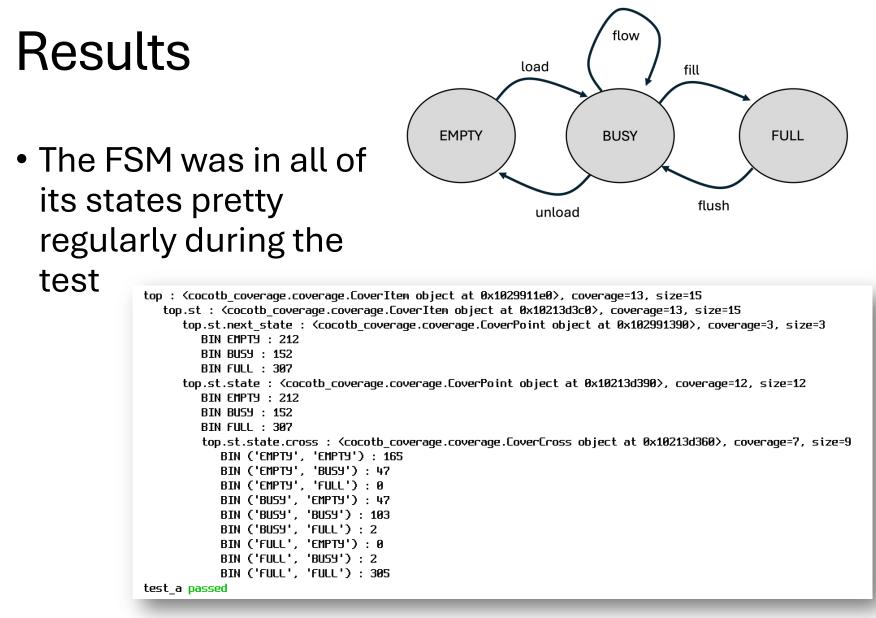

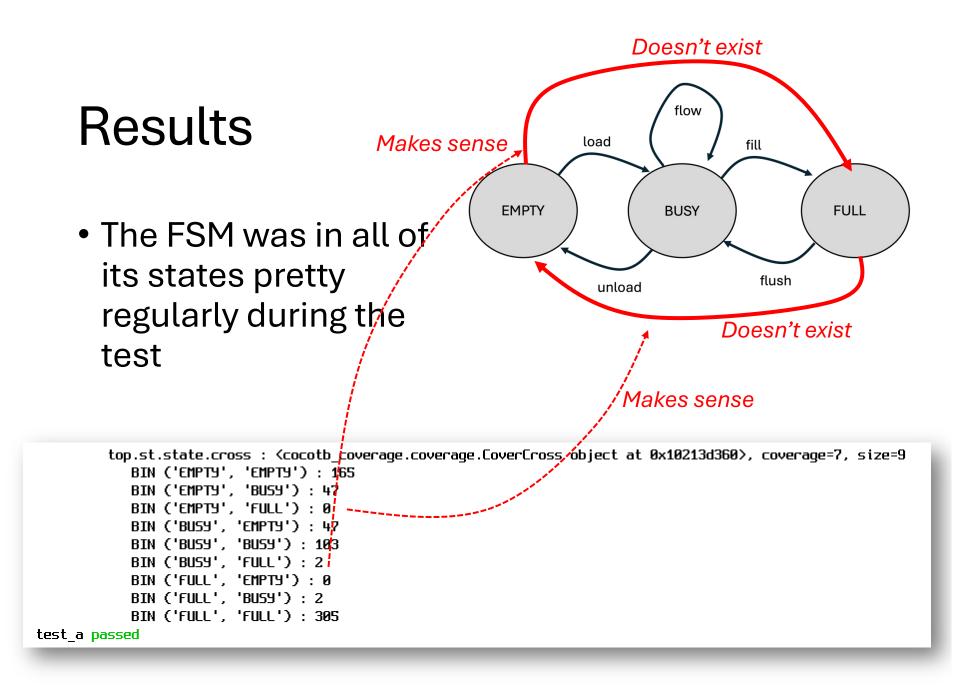

#### Results

- It does seem to have some "coverage" of the input space

- but how much of that is relevant or not relevant.

| top.st sig : <cocotb 0x106ce9b40="" at="" coverage.coverage.coveritem="" object="">, coverage=23, size=59</cocotb>        |

|---------------------------------------------------------------------------------------------------------------------------|

| top.st sig.cross : <cocotb 0x106cea200="" at="" coverage.coverage.covercross="" object="">, coverage=12, size=48</cocotb> |

| BIN ('EMP19', Irue, Irue, Irue, Irue) : 0                                                                                 |

| BIN ('EMPTY', True, True, True, False) : 0                                                                                |

| BIN ('EMPTY', True, True, False, True) : 178                                                                              |

| BIN ('EMPTY', True, True, False, False) : 541                                                                             |

| BIN ('EMPTY', True, False, True, True) : 0                                                                                |

| BIN ('EMPTY', True, False, True, False) : 0                                                                               |

| BIN ('EMPTY', True, False, False, True) : 0                                                                               |

| BIN ('EMPTY', True, False, False, False) : 0                                                                              |

| BIN ('EMPTY', False, True, True, True): 0                                                                                 |

| BIN ('EMPTY', False, True, True, False) : 0                                                                               |

| BIN ('EMPTY', False, True, False, True) : 854                                                                             |

| BIN ('EMPTJ', False, True, False, False) : 1645                                                                           |

| BIN ('EMPT', False, False, True, True): 0                                                                                 |

| BIN ('EMPT', False, False, True, False) : 0                                                                               |

| BIN ('EMPT'), False, False, False, True) : 0                                                                              |

| BIN ('EMPT3', False, False, False, False) : 0                                                                             |

| BIN ('BUS', True, True, True, True, 1:233                                                                                 |

| BIN (BUSS', True, True, False) : 761                                                                                      |

| BIN ('BUSY', True, True, False, True) : 0                                                                                 |

| BIN ('BUSY', True, True, False, False) : 0                                                                                |

| BIN (1905), True, False, True, True, 1:0                                                                                  |

| BIN ('BUSY', True, False, True, False) : 0                                                                                |

| BIN ('BUSY', True, False, False, True) : 0                                                                                |

| BIN ('BUSS', True, False, False, False) : 0                                                                               |

| BIN ('BUSS', False, True, True) : 719                                                                                     |

| BIN ('BUSY', False, True, True, False) : 2335                                                                             |

| BIN ('BUSY', False, True, False, True) : 0                                                                                |

| BIN ('BUS', False, True, False, False) : 0                                                                                |

| BIN ('BUSY', False, False, True, True) : 0                                                                                |

| BIN ('BUSY', False, False, True, False) : 0                                                                               |

| BIN ('BUSY', False, False, False, True) : 0                                                                               |

| BIN ('BUSY', False, False, False, False) : 0                                                                              |

| BIN ('FULL', True, True, True, True) : 0                                                                                  |

| BIN (FULL', True, True, True, False) : 0                                                                                  |

| BIN (FULL', True, True, False, True) : 0                                                                                  |

| BIN ('FULL', True, True, False, False) : 0                                                                                |

| BIN ('FULL', True, False, True, True) : 190                                                                               |

| BIN ('FULL', True, False, True, False) : 563                                                                              |

|                                                                                                                           |

| BIN ('FULL', True, False, False, True) : 0                                                                                |

| BIN ('FULL', True, False, False, False) : 0                                                                               |

| BIN ('FULL', False, True, True, True): 0                                                                                  |

| BIN ('FULL', False, True, True, False) : 0                                                                                |

| BIN ('FULL', False, True, False, True) : 0                                                                                |

| BIN ('FULL', False, True, False, False) : 0                                                                               |

| BIN ('FULL', False, False, True, True) : 571                                                                              |

| BIN ('FULL', False, False, True, False) : 1711                                                                            |

| BIN ('FULL', False, False, False, True) : 0                                                                               |

| BIN ('FULL', False, False, False, False) : 0                                                                              |

#### At the naïve level...

• Yes there are 48 possible state transitions and things, but as Jordan confidently pointed out on Monday, the state controls some of these signals, so that seems maybe a little excessive.

#### Change the Crosses

• There's likely no reason (at least at this point) to have the signals on both sides mixed together in one large coverage cross

#### Result Slave Cross:

#### (STATE, VALID, READY)

top.st\_sig.scross : <cocotb\_coverage.coverage.CoverCross object at 0x103275810>, coverage=6, size=12

BIN ('EMPTY', True, True) : 11

BIN ('EMPTY', True, False) : 0

BIN ('EMPTY', False, True) : 711

BIN ('EMPTY', False, False) : 0

BIN ('BUSY', True, True) : 103

BIN ('BUSY', True, False) : 0

BIN ('BUSY', False, True) : 35

BIN ('BUSY', False, False) : 0

BIN ('FULL', True, True) : 0

BIN ('FULL', True, False) : 12

#### Master Cross:

(STATE, VALID, READY)

top.st\_sig.mcross : <cocotb\_coverage.coverage.CoverCross object at 0x103276350>, coverage=6, size=12

BIN ('EMPTY', True, True) : 0

BIN ('EMPTY', False, True) : 485

BIN ('EMPTY', False, False) : 237

BIN ('BUSY', True, True) : 67

BIN ('BUSY', True, True) : 67

BIN ('BUSY', False, True) : 0

BIN ('BUSY', False, True) : 0

BIN ('FULL', True, True) : 47

BIN ('FULL', True, False) : 94

BIN ('FULL', False, False) : 0

BIN ('FULL', False, False) : 0

- Some of these cross values should not be achieved:

- s00\_axis\_tready never 0 in EMPTY

- m00\_axis\_tvalid never 0 in FULL

m00 axis tvalid <= 1;

54 55

57

59

60

61

62

63

64

69

70

71

72

73

74

75

76

77

78

79

80

end

end

endcase

end

end

default: begin

state <= EMPT9;</pre>

## Result

Should Not Occur:

Slave Cross:

s00 axis tready never 0 in EMPTY m00 axis tvalid never 0 in FULL

#### (STATE, VALID, READY)

top.st sig.scross : <cocotb coverage.coverage.CoverCross object at 0x103275810>, coverage=6, size=12 🔽 BIN ('EMPTY', True, True) : 11 🚫 BIN ('EMPTY', True, False) : 0 🔽 BIN ('EMPTY', False, True) : 711 🚫 BIN ('EMPTY', False, False) : 0 🔽 BIN ('BUSY', True, True) : 103 🔽 BIN ('BUSY', True, False) : 0 BIN ('BUSY', False, True) : 35 🔽 BIN ('BUSY', False, False) : 0 BIN ('FULL', True, True) : 0 BIN ('FULL', True, False) : 129 🔽 BIN ('FULL', False, True) : 0 II BIN ('FULL', False, False) : 12

wtf

#### Master Cross:

(STATE, VALID, READY)

top.st sig.mcross : <cocotb coverage.coverage.CoverCross object at 0x103276350>, coverage=6, size=12 BIN ('EMPTY', True, True) : 0 BIN ('EMPTY', True, False) : 0 BIN ('EMPTY', False, True) : 485 BIN ('EMPTY', False, False) : 237 BIN ('BUSY', True, True) : 67 BIN ('BUSY', True, False) : 71 BIN ('BUSY', False, True) : 0 BIN ('BUSY', False, False) : 0 BIN ('FULL', True, True) : 47 BIN ('FULL', True, False) : 94 BIN ('FULL', False, True) : 0 BIN ('FULL', False, False) : 0

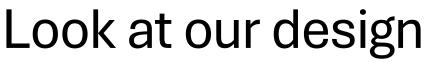

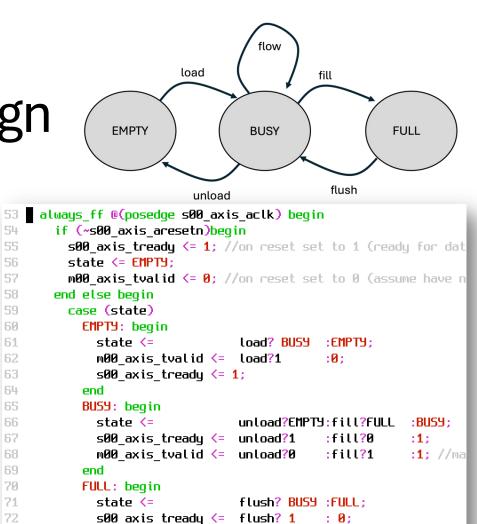

#### Look at our design

- Some of these cross values should not be achieved :

- s00\_axis\_tready never 0

when was EMPTY

- m00\_axis\_tvalid never 0

when was FULL

# Should these be achievable?

Legit/Might Occur: Should Not Occur:

(OLD STATE, VALID, READY)

#### Slave Cross:

#### top.st\_sig.scross : <cocotb\_coverage.coverage.CoverCross object at 0x105555810>, coverage=10, size=12 V BIN ('EMPTY', True, True) : 15 🚫 BIN ('EMPTY', True, False) : 0🔨 🔽 BIN ('EMPTY', False, True) : 815 🚫 BIN ('EMPTY', False, False) : 0 ┥ 🔽 BIN ('BUSY', True, True) : 23 If I was previously EMPTY 🔽 BIN ('BUSY', True, False) : 29 there's no way READY would 🔽 BIN ('BUSY', False, True) : 18 🔽 BIN ('BUSY', False, False) : 4 be 0 now 🗸 BIN ('FULL', True, True) : 29 🗸 BIN ('FULL'. True. False) : 53 🗹 BIN ('FULL', False, True) : 4 🗹 BIN ('FULL', False, False) : 11

#### Master Cross:

#### (OLD\_STATE, VALID, READY)

top.st\_sig.mcross : <cocoth\_coverage.coverage.CoverCross object at 0x105556350>, coverage=10, size=12

V BIN ('EMPT9', True, True) : 7

BIN ('EMPT9', False, True) : 740

BIN ('EMPT9', False, False) : 82

BIN ('BUS9', True, True) : 20

BIN ('BUS9', True, False) : 46

BIN ('BUS9', False, True) : 3

BIN ('BUS9', False, True) : 3

BIN ('BUS9', False, False) : 5

BIN ('FULL', True, True) : 40

BIN ('FULL', True, False) : 57

BIN ('FULL', False, True) : 0

BIN ('FULL', False, False) : 6

BIN ('FULL', Fals

## Another Big Issue

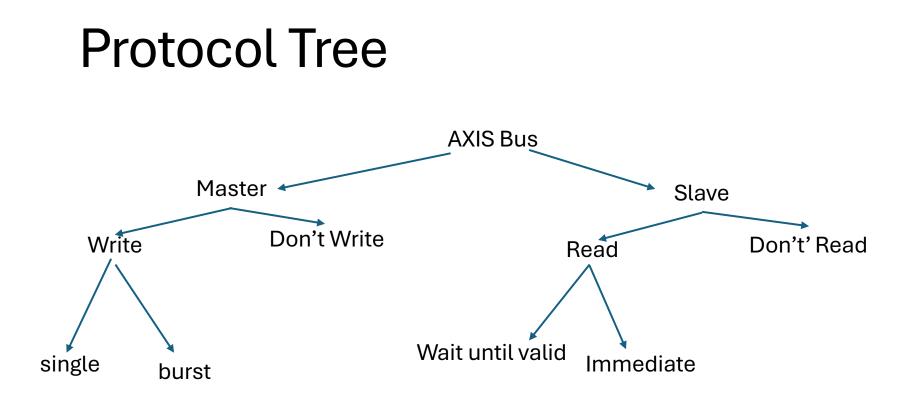

- AXI is about more than just the value at any point in time.

- As pointed out in class on Monday, AXI as a protocol has rules and those are rules are inherently stateful.

- Just throwing random values at the busses with no regard for history/meaning could be wrong:

- Giving it illegal values

- Wasting cycles testing stuff that shouldn't be tested

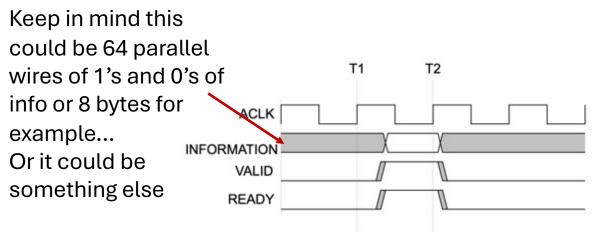

### **Generalized Transaction**

- All Channel Interactions follow same high-level structure

- Data is handed off IF AND ONLY IF VALID and READY are high on the rising edge of the clock

- If that happens, both parties must realize that data transfer has happened

Figure A3-4 VALID with READY handshake

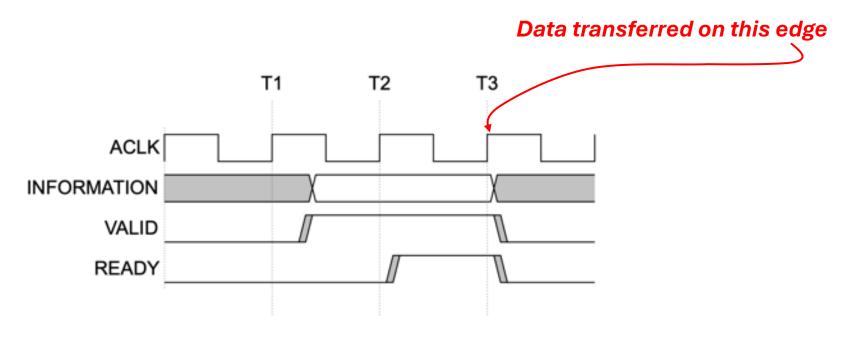

## VALID then READY

- Valid can be high first

- Then ready can show up later

- Only when both are high is data exchanged

Figure A3-2 VALID before READY handshake

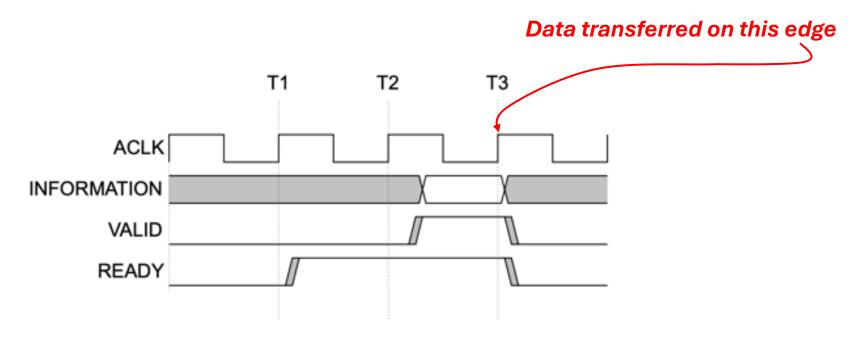

### **READY then VALID**

- Ready can be high first

- Then Valid can show up later

- Only when both are high is data exchanged

Figure A3-3 READY before VALID handshake

https://fpga.mit.edu/6205/F24

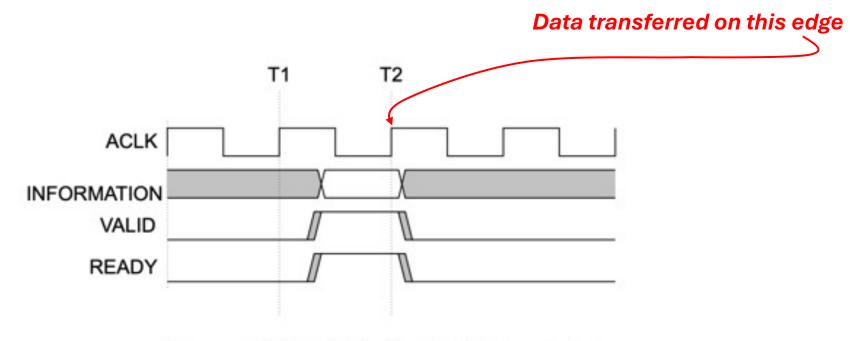

## READY WITH VALID

- Ready and Valid come high at the same time

- Totally allowed

- Data is exchanged on that clock edge

#### Figure A3-4 VALID with READY handshake

https://fpga.mit.edu/6205/F24

### IMPORTANT

- the VALID signal of the AXI interface sending information *must not be dependent* on the READY signal of the AXI interface receiving that information

- an AXI interface that is receiving information *may* wait until it detects a **VALID** signal before it asserts its corresponding **READY** signal.

- In other words **READY** can depend on **VALID**, but not the other way around.

- Once **VALID** is asserted, it cannot be deasserted until **READY** has also been asserted for at least one cycle

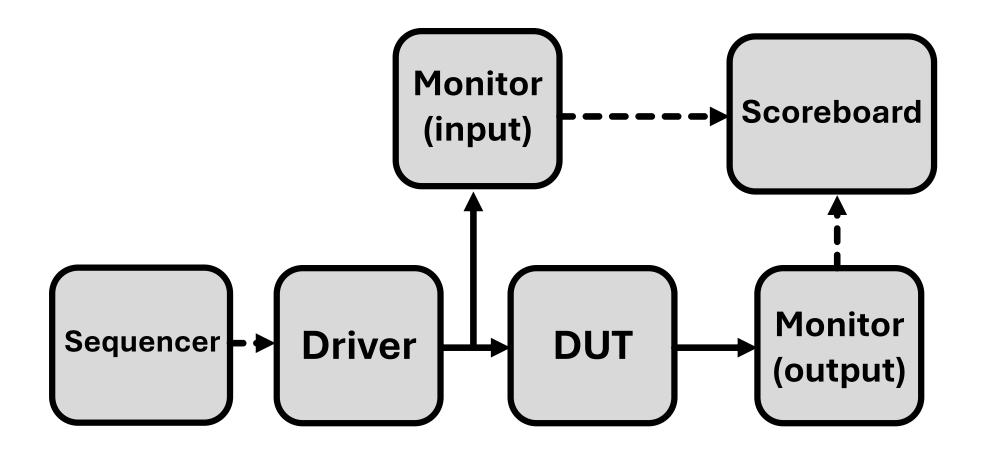

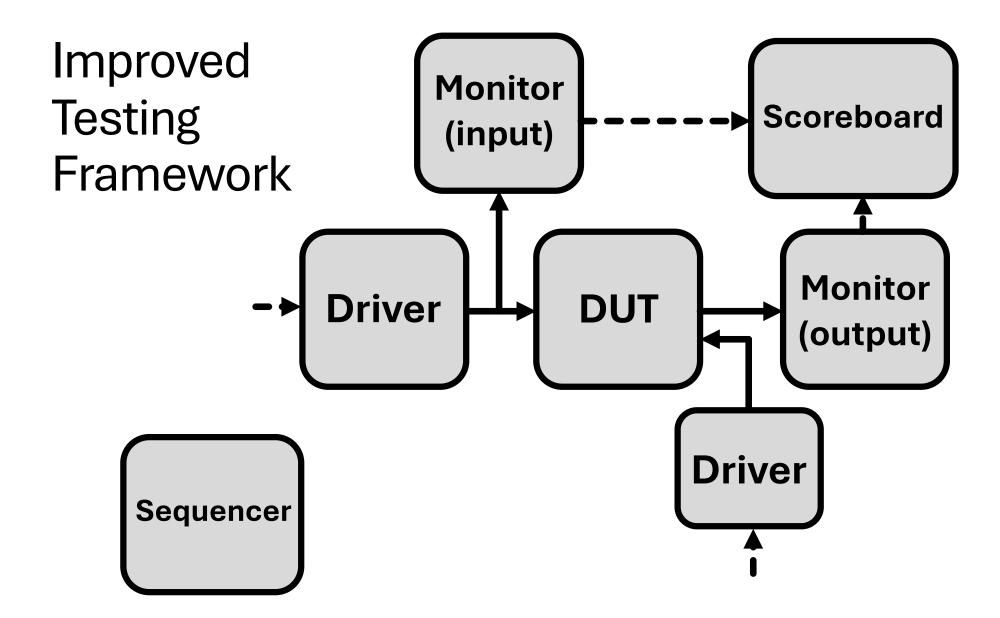

#### **Standard Testing Framework**

## Right now...

Kind just fudging the ready signal, but really we should try to more intelligently probe this thing @cocotb.test()

async def test\_a(dut):

"""cocotb test for averager controller"""

```

tester = SBTester(dut)

tester.start()

cocotb.start_soon(Clock(dut.s00_axis_aclk, 10, units="ns").start())

cocotb.start_soon(state_monitor(dut))

cocotb.start_soon(sts_monitor(dut))

await set_ready(dut,1)

await reset(dut.s00_axis_aclk, dut.s00_axis_aresetn,2,0)

```

feed the driver: for i in range(50): data = {'type':'single', "contents":{"data": random.randint(1,255),"last": tester.input\_driver.append(data) #data = {'type':'burst', "contents":{"data": np.array(20\*[0]+[1]+30\*[0]+[-2] data = {'type':'burst', "contents":{"data": np.array(list(range(100)))}} tester.input\_driver.append(data) await ClockCycles(dut.s00\_axis\_aclk, 50) await set\_ready(dut,0) await set\_ready(dut,0) await set\_ready(dut,1) await ClockCycles(dut.s00\_axis\_aclk, 10) await set\_ready(dut,0) await set\_ready(dut,0) await set\_ready(dut,0) await set\_ready(dut,0) await set\_ready(dut,1)

await ClockCycles(dut.s00\_axis\_aclk, 300)

# What we'd really like is something to coordinate

#### So let's maybe rewrite our Driver

• Driver can now be for a Master or a Slave

```

class RXISDriver(BusDriver):

def __init__(self, dut, name, clk,type='M'):

self._signals = ['axis_tvalid', 'axis_tready', 'axis_tlast', 'axis_tdata', 'axis_tstrb']

BusDriver.__init__(self, dut, name, clk)

self.clock = clk

self.type = type

if self.type=="M": #set data, strb, last and valid)

self.bus.axis_tdata.value = 0

self.bus.axis_ttata.value = 0

self.bus.axis_tstrb.value = 0

self.bus.axis_tlast.value = 0

self.bus.axis_tvalid.value = 0

else: #must be slave (only set ready)

self.bus.axis_tready.value = 0

```

# Add an output\_driver to our Tester class

```

class SBTester:

.....

Checker of a Skid Buffer instance

Args

dut_entity: handle to an instance of skid_buffer

.....

def init (self, dut entity: SimHandleBase, debug=False):

self.dut = dut entity

self.log = logging.getLogger("cocotb.tb")

self.log.setLevel(logging.DEBUG)

self.input mon = AXISMonitor(self.dut,'s00',self.dut.s00 axis aclk, callback=self.model)

self.output mon = AXISMonitor(self.dut,'m00',self.dut.s00 axis aclk)

self.input driver = AXISDriver(self.dut,'s00',self.dut.s00 axis aclk,tupe='M')

self.output driver = AXISDriver(self.dut,'m00',self.dut.s00 axis aclk,tupe='5')

self. checker = None

self.calcs sent = 0

# Create a scoreboard on the stream out bus

self.expected output = [] #contains list of expected outputs (Growing)

self.scoreboard = Scoreboard(self.dut,fail immediately=False)

self.scoreboard.add interface(self.output mon, self.expected output)

```

#### Now feed in random, legal transactions to both the valid and readv side

```

async def test a(dut):

"""cocotb test for averager controller""

tester = SBTester(dut)

tester.start()

cocotb.start soon(Clock(dut.s00 axis aclk, 10, units="ns").start())

cocotb.start soon(state monitor(dut))

cocotb.start soon(sts monitor(dut))

cocotb.start soon(os monitor(dut))

#await set ready(dut,1)

await reset(dut.s00 axis aclk, dut.s00 axis aresetn,2,0)

#feed the M driver:

for i in range(100):

wtype = 'write' if random.random()<0.5 else 'no write'</pre>

duration = random.randint(0,100)

tlast = random.random()>0.5

length = random.randint(1,10)

data = [random.randint(0,65535) for i in range(length)]

w data = {'type':wtype, "duration":duration, "contents":{"data": data},"tlast":tlast}

tester.input driver.append(w data)

for i in range(1000):

rtupe = 'read' if random.random()<0.5 else 'no read'</pre>

immediate = random.random()<0.5</pre>

duration = random.randint(0,2)

wait duration = random.randint(0,3)

r_data = {'type':rtype, "immediate": immediate, "wait_duration":wait_duration, "duration":duration}

tester.output driver.append(r data)

data = {'type':'read', "immediate": True, "wait duration":0, "duration":500} #just to empty it

tester.output driver.append(data)

```

### Make a New "higher level" Cover section

- This one will track cycle-to-cycle transitions of the valid and ready signals on both ports

- No reason to combine the two ports really...there's nothing about the spec anyways

```

CoverPoint("top.os.s00 tvalid",

xf=lambda sig: sig.get('s00 tvalid'),

bins=['V:0->0', 'V:0->1', 'V:1->0', 'V:1->1']

).

CoverPoint("top.os.s00 tready",

xf=lambda sig: sig.get('s00 tready'),

bins=['R:0->0', 'R:0->1', 'R:1->0', 'R:1->1']

),

CoverPoint("top.os.m00 tvalid",

xf=lambda sig: sig.get('m00 tvalid'),

bins=['V:0->0', 'V:0->1', 'V:1->0', 'V:1->1']

),

CoverPoint("top.os.m00 tready",

xf=lambda sig: sig.get('m00 tready'),

bins=['R:0->0', 'R:0->1', 'R:1->0', 'R:1->1']

Э.

CoverCross("top.os.s cross",

items=[ "top.os.s00 tvalid",

"top.os.s00 tready"]

Э.

CoverCross("top.os.m cross",

items=[ "top.os.m00 tvalid",

"top.os.m00 tready"]

)

)

```

# Make support functions

• Track and Label transitions of all four signals over time.

```

async def os monitor(dut):

read only = ReadOnly()

falling edge = FallingEdge(dut.s00 axis aclk)

rising edge = RisingEdge(dut.s00 axis aclk)

await read only

olds = get rv(dut)

while True:

await falling edge #when module would change

await read only

news = get rv(dut)

siq = {}

for i in ['s00 tvalid','s00 tready','m00 tvalid','m00 tready']:

if 'v' in i:

sig[i] = 'V:'+match(olds[i],news[i])

else:

sig[i] = 'R:'+match(olds[i],news[i])

os sampling function(sig)

olds = news # remember for future compare

```

```

def match(old,new):

outstr = ''

if old:

outstr+='1'

else:

outstr+='0'

outstr += '->'

if new:

outstr+='1'

else:

outstr+='1'

return outstr

```

def get\_rv(dut):

#### Run it

| ▶ ▶ ₩   I← →I   └─ O   Ħ ⊑ | しつ ひ                                                                       |                             |           |

|----------------------------|----------------------------------------------------------------------------|-----------------------------|-----------|

| C_M00_AXIS_TDATA_WIDTH     | (00000020                                                                  |                             |           |

| <br>C_S00_AXIS_TDATA_WIDTH | (00000020                                                                  |                             |           |

| lata_buffer_wren           |                                                                            |                             |           |

| lata_out_wren              |                                                                            |                             |           |

| u                          |                                                                            |                             |           |

| low                        |                                                                            |                             | 000 00    |

| ush                        |                                                                            |                             |           |

| isert                      |                                                                            |                             |           |

| ad                         |                                                                            |                             |           |

| nload                      |                                                                            |                             |           |

| se_buffered_data           |                                                                            |                             |           |

| emove                      |                                                                            |                             |           |

| 100_axis_aclk              |                                                                            |                             |           |

| 100_axis_aresetn           |                                                                            |                             |           |

| n00_axis_tdata [31:0]      | 3                                                                          | 7 🛛 🗶 3 🗶 1 🗶 44714 🗶 61898 | 8 33027   |

| n00_axis_tlast             |                                                                            |                             |           |

| n00_axis_tvalid            |                                                                            |                             |           |

| n00_axis_tready            |                                                                            |                             |           |

| n00_axis_tstrb [3:0]       | (f                                                                         |                             |           |

| 00_axis_aclk               |                                                                            |                             |           |

| 00_axis_aresetn            |                                                                            |                             |           |

| 00_axis_tdata [31:0]       | 3                                                                          | 3 1 44714 61898             | 8 33027   |

| 00_axis_tvalid             |                                                                            |                             |           |

| 00_axis_tready             |                                                                            |                             |           |

| tate [31:0]                |                                                                            |                             | XXX0 XXX0 |

| 00_axis_tlast              |                                                                            |                             |           |

| 00_axis_tstrb [3:0]        | (f                                                                         |                             |           |

| data_buffer [31:0]         | (1) (X) 5465 (X) () (X) 39875 (X)) (X) 38049 (28976 (49) 1653 (X) (X) 7677 | 7 39452                     |           |

| last_buffer                |                                                                            |                             |           |

| strb_buffer [3:0]          | (f                                                                         |                             |           |

10/23/24

#### Run it and you get...

| top.os.s_cross : <cocotb_coverage.coverage.covercross 0x1068863b0="" at="" object="">, coverage=10, size=16</cocotb_coverage.coverage.covercross>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BIN ('V:0->0', 'R:0->0') : 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| BIN ('V:0->0', 'R:0->1') : 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| BIN ('V:0->0', 'R:1->0') : 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| BIN ('V:0->0', 'R:1->1') : 9372                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| BIN ('V:0->1', 'R:0->0') : 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| BIN ('V:0->1', 'R:0->1') : 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| BIN ('V:0->1', 'R:1->0') : 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| BIN ('V:0->1', 'R:1->1') : 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| BIN ('V:1->0', 'R:0->0') : 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| BIN ('V:1->0', 'R:0->1') : 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| BIN ('V:1->0', 'R:1->0') : 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| BIN ('V:1->0', 'R:1->1') : 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| BIN ('V:1->1', 'R:0->0') : 280                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| BIN ('V:1->1', 'R:0->1') : 35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| BIN ('V:1->1', 'R:1->0') : 35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| BIN ('V:1->1', 'R:1->1') : 222                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| top.os.m_cross : <cocotb_coverage.coverage.covercross 0x106886710="" at="" object="">, coverage=12, size=16</cocotb_coverage.coverage.covercross>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| BIN ('V:0->0', 'R:0->0') : 550                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| BIN ('U:0->0', 'R:0->0') : 550<br>BIN ('U:0->0', 'R:0->1') : 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| BIN ('V:0->0', 'R:0->0') : 550<br>BIN ('V:0->0', 'R:0->1') : 1<br>BIN ('V:0->0', 'R:1->0') : 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| BIN ('V:0->0', 'R:0->0') : 550<br>BIN ('V:0->0', 'R:0->1') : 1<br>BIN ('V:0->0', 'R:1->0') : 1<br>BIN ('V:0->0', 'R:1->1') : 8792                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| BIN ('V:0->0', 'R:0->0') : 550<br>BIN ('V:0->0', 'R:0->1') : 1<br>BIN ('V:0->0', 'R:1->0') : 1<br>BIN ('V:0->0', 'R:1->1') : 8792<br>BIN ('V:0->1', 'R:0->0') : 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| BIN ('V:0->0', 'R:0->0') : 550<br>BIN ('V:0->0', 'R:0->1') : 1<br>BIN ('V:0->0', 'R:1->0') : 1<br>BIN ('V:0->0', 'R:1->1') : 8792<br>BIN ('V:0->1', 'R:0->0') : 3<br>BIN ('V:0->1', 'R:0->1') : 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| BIN ('V:0->0', 'R:0->0') : 550<br>BIN ('V:0->0', 'R:0->1') : 1<br>BIN ('V:0->0', 'R:1->0') : 1<br>BIN ('V:0->0', 'R:1->1') : 8792<br>BIN ('V:0->1', 'R:0->0') : 3<br>BIN ('V:0->1', 'R:0->1') : 0<br>BIN ('V:0->1', 'R:1->0') : 0                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| BIN ('V:0->0', 'R:0->0') : 550<br>BIN ('V:0->0', 'R:0->1') : 1<br>BIN ('V:0->0', 'R:1->0') : 1<br>BIN ('V:0->0', 'R:1->1') : 8792<br>BIN ('V:0->1', 'R:0->0') : 3<br>BIN ('V:0->1', 'R:0->1') : 0<br>BIN ('V:0->1', 'R:1->0') : 0<br>BIN ('V:0->1', 'R:1->1') : 19                                                                                                                                                                                                                                                                                                                                                                                                                          |

| BIN ('V:0->0', 'R:0->0') : 550<br>BIN ('V:0->0', 'R:0->1') : 1<br>BIN ('V:0->0', 'R:1->0') : 1<br>BIN ('V:0->0', 'R:1->1') : 8792<br>BIN ('V:0->1', 'R:0->0') : 3<br>BIN ('V:0->1', 'R:0->1') : 0<br>BIN ('V:0->1', 'R:1->1') : 0<br>BIN ('V:0->1', 'R:1->1') : 19<br>BIN ('V:0->1', 'R:0->0') : 0                                                                                                                                                                                                                                                                                                                                                                                          |